電路板(ban)是(shi)如(ru)何(he)設計(ji)出來?什麽樣(yang)的(de)電路板(ban)設計(ji)很厲(li)害?

- 發(fa)表時間(jian):2021-06-23 15:45:34

- 來源:本站(zhan)

- 人氣:886

本(ben)文(wen)《電(dian)路板(ban)是(shi)如(ru)何(he)設計(ji)出來?什麽樣(yang)的(de)電路板(ban)設計(ji)很厲(li)害?》是(shi)深(shen)圳市潤(run)澤(ze)五(wu)洲(zhou)電子科(ke)技有(you)限(xian)公(gong)司PCBA作(zuo)者編(bian)輯(ji),深(shen)圳市潤(run)澤(ze)五(wu)洲(zhou)電子科(ke)技有(you)限(xian)公(gong)司是(shi)壹(yi)家專(zhuan)註PCBA設計(ji)制造(zao)的民族企業(ye),服(fu)務(wu)於國內(nei)外眾(zhong)多新(xin)能源,汽車電子、安防電子(zi)、智能玩具(ju)、智(zhi)能家居(ju)、小(xiao)家(jia)電(dian)等各(ge)行(xing)業(ye)客(ke)戶,是壹(yi)家集(ji)方案(an)設計(ji)、電子(zi)元(yuan)器(qi)件(jian)代采、SMT貼片加(jia)工及(ji)測(ce)試組(zu)裝的(de)壹(yi)站式(shi)制造(zao)服務(wu)商。

我(wo)們先簡(jian)單(dan)的描述(shu)壹(yi)下電(dian)路(lu)板(ban)是(shi)如(ru)何(he)設計(ji)出來的

1、首(shou)先是(shi)選(xuan)型,選(xuan)型的意(yi)思就是選(xuan)擇我(wo)們電(dian)路(lu)板(ban)電(dian)路(lu)裏面所用到(dao)的(de)電子元(yuan)器(qi)件(jian)。

電(dian)子(zi)元(yuan)器(qi)件(jian)分為(wei)很多種(zhong),常(chang)見(jian)的有(you)電(dian)阻(zu)、電容(rong)、IC等,都有(you)各(ge)種(zhong)耐壓各(ge)種(zhong)封裝的(de)電(dian)子元(yuan)器(qi)件(jian),做(zuo)電(dian)路板(ban)設計(ji)首先需要(yao)選(xuan)擇我(wo)們應(ying)該(gai)在(zai)板(ban)子(zi)上放什(shen)麽(me)樣(yang)的(de)元(yuan)電(dian)子(zi)器(qi)件(jian),是插件(jian)的還(hai)是(shi)貼片的(de)電(dian)子元(yuan)件(jian)等等(deng)。

2、選(xuan)好每(mei)個(ge)電子(zi)元(yuan)器(qi)件(jian)的型號(hao)之後(hou)就可以(yi)進行(xing)電路(lu)原(yuan)理圖(tu)的設計(ji)了。

原(yuan)理圖(tu)設計(ji)需要(yao)用到(dao)壹(yi)些常(chang)用的原理圖(tu)設計(ji)軟(ruan)件(jian),比如(ru)orCAD。其實(shi)每(mei)個(ge)原理圖(tu)設計(ji)軟(ruan)件(jian)都是大(da)同小(xiao)異(yi),步(bu)驟方(fang)法(fa)都是差(cha)不(bu)多(duo)的。下(xia)面(mian)帶(dai)妳了解(jie)原(yuan)理圖(tu)的設計(ji)的簡(jian)單(dan)步驟。

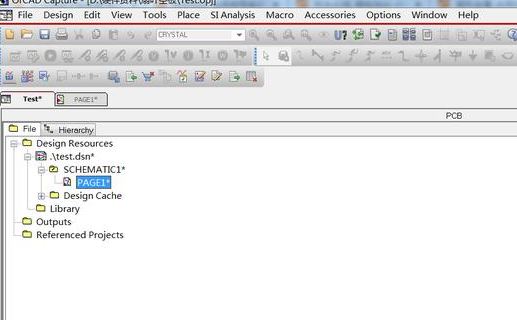

(1)打(da)開orCAD設計(ji)軟(ruan)件(jian),單擊(ji)【File】,選(xuan)擇【New】,選(xuan)擇【Project】,新(xin)建(jian)壹(yi)個(ge)項(xiang)目(mu)工程(cheng)文件(jian),如(ru)圖所(suo)示(shi)壹(yi)個(ge)新(xin)的(de)工程(cheng)文件(jian)創建成(cheng)功(gong)了(le)。

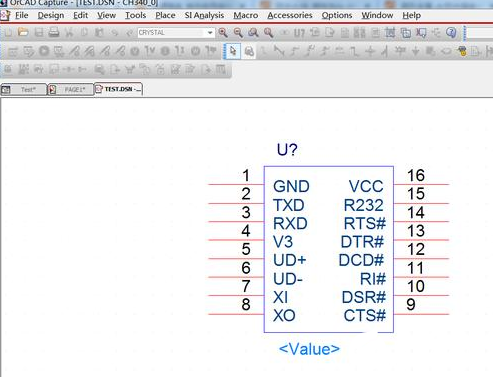

(2)原(yuan)理圖(tu)庫裏面沒(mei)有(you)的(de)元(yuan)件(jian)封裝先創建壹(yi)個(ge)原理圖(tu)庫,方法(fa)是(shi)單擊(ji)【File】,選(xuan)擇【New】,選(xuan)擇【Library】,然(ran)後(hou)根(gen)據電(dian)子元(yuan)器(qi)件(jian)的數(shu)據(ju)手冊(ce)放置對(dui)應(ying)的引(yin)腳(jiao)即可(ke)。

(3)從(cong)軟(ruan)件(jian)自(zi)帶的(de)元(yuan)器(qi)件(jian)庫裏面調(tiao)用(yong)封裝庫,在(zai)原(yuan)理圖(tu)繪圖區域(yu)合適(shi)的位(wei)置擺(bai)放元(yuan)件(jian)符號(hao),單擊(ji)【Place】,然(ran)後(hou)單(dan)【Part】即(ji)可(ke)放置元(yuan)器(qi)件(jian),如(ru)圖所(suo)示(shi)。

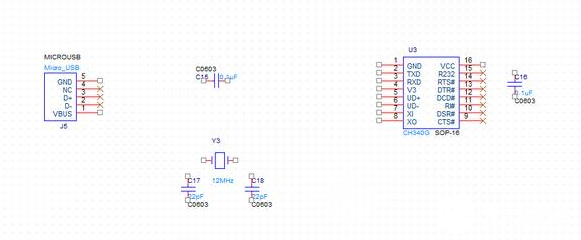

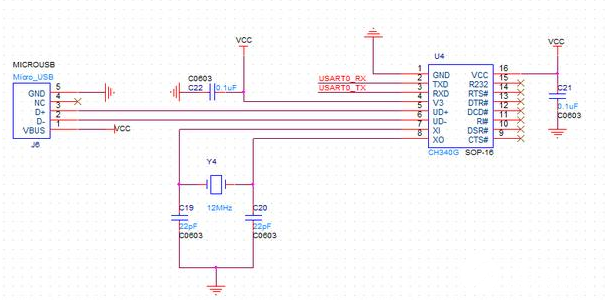

(4)將(jiang)各(ge)個(ge)元(yuan)件(jian)用導(dao)線連(lian)接(jie)起(qi)來,使得(de)每(mei)個(ge)元(yuan)器(qi)件(jian)之間(jian)形(xing)成(cheng)壹(yi)個(ge)個(ge)的電(dian)路回(hui)路,如(ru)圖所(suo)示(shi)。

USB轉TTL

最後給(gei)每(mei)個(ge)元(yuan)器(qi)件(jian)添(tian)加(jia)上封裝信息就可以(yi)完(wan)成原(yuan)理圖(tu)的設計(ji)過程(cheng)了(le),設計(ji)好了原理圖(tu)之後(hou)就生產(chan)壹(yi)個(ge).asc的網(wang)表文件(jian),原理圖(tu)的設計(ji)就是為(wei)了(le)得(de)到(dao)這個(ge)網表文件(jian),而這個(ge)網表文件(jian)是PCB各(ge)個(ge)元(yuan)件(jian)連(lian)接(jie)的橋(qiao)梁(liang),至(zhi)關(guan)重要(yao),關(guan)乎設計(ji)的成(cheng)敗(bai)。

3、PCB設計(ji)(PrintedCircuitBoard,也就是印制電路板(ban)的(de)意(yi)思),最後進行(xing)PCB設計(ji)就可以(yi)完(wan)成整(zheng)個(ge)電路(lu)板(ban)的(de)設計(ji)過程(cheng)了(le)。

PCB設計(ji)可以(yi)大致(zhi)分為五(wu)個(ge)步驟(zhou):元(yuan)器(qi)件(jian)封裝庫設計(ji)、元(yuan)件(jian)布局(ju)、布(bu)線、優化(hua)、DRC檢(jian)查。下面就是壹(yi)個(ge)設計(ji)好的簡(jian)單(dan)的PCB文件(jian),通(tong)過(guo)這個(ge)設計(ji)好的文件(jian)相關(guan)的(de)資(zi)料發(fa)送(song)到(dao)板(ban)廠(chang)就可以(yi)幫我(wo)們做(zuo)出來這個(ge)電路(lu)板(ban)了(le)。

單(dan)板(ban)PCB

需要(yao)PCB外發(fa)做(zuo)回(hui)來的電(dian)路板(ban)是(shi)空(kong)的,也就是沒(mei)有(you)貼電子(zi)元(yuan)器(qi)件(jian)的,這個(ge)時候(hou)就需要(yao)我們自(zi)己(ji)或(huo)者讓工廠(chang)將電(dian)子(zi)元(yuan)器(qi)件(jian)焊接(jie)到(dao)空(kong)的電(dian)路(lu)板(ban)上就可以(yi)完(wan)成電(dian)路板(ban)的(de)制作了。

接(jie)下來(lai)看下(xia)如(ru)何(he)布線(xian)電(dian)路(lu)板(ban)設計(ji)算(suan)是(shi)很厲(li)害的(de)

1、如(ru)果(guo)設計(ji)的電(dian)路(lu)系(xi)統(tong)中包(bao)含FPGA器(qi)件(jian),則在(zai)繪制原理圖(tu)前必需使用(yong)Quartus II軟(ruan)件(jian)對管(guan)腳(jiao)分配(pei)進行(xing)驗(yan)證。(FPGA中某(mou)些特(te)殊的管腳(jiao)是不(bu)能用作普通(tong)IO的(de))

2、4層板(ban)從(cong)上到(dao)下(xia)依次為:信號(hao)平(ping)面層、地、電源、信號(hao)平(ping)面層;6層板(ban)從(cong)上到(dao)下(xia)依次為:信號(hao)平(ping)面層、地、信號(hao)內(nei)電層、信號(hao)內(nei)電層、電源、信號(hao)平(ping)面層。6層以(yi)上板(ban)(優點是:防幹(gan)擾輻射),優先選(xuan)擇內(nei)電層走(zou)線,走(zou)不開選(xuan)擇平(ping)面層,禁止(zhi)從(cong)地或電(dian)源層走(zou)線(原(yuan)因(yin):會分割(ge)電源層,產生(sheng)寄生效(xiao)應)。

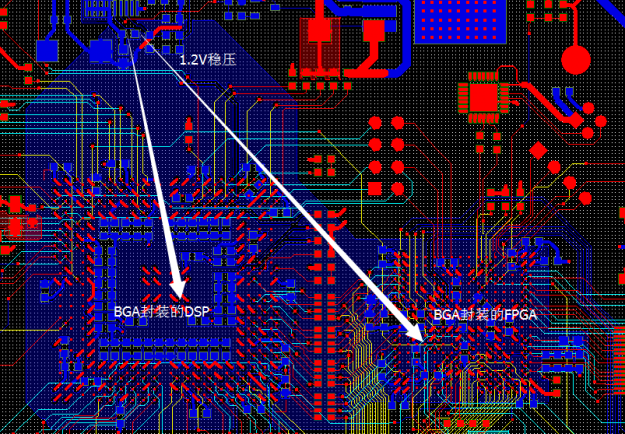

3、多電源系(xi)統(tong)的布(bu)線:如(ru)FPGA+DSP系(xi)統(tong)做(zuo)6層板(ban),壹(yi)般至少會有(you)3.3V+1.2V+1.8V+5V。

3.3V壹(yi)般是主電源,直接(jie)鋪電源層,通(tong)過(guo)過(guo)孔(kong)很容(rong)易(yi)布(bu)通(tong)全局(ju)電(dian)源網絡(luo)。

5V壹(yi)般可能是電源輸入(ru),只(zhi)需要(yao)在(zai)壹(yi)小(xiao)塊(kuai)區(qu)域(yu)內(nei)鋪銅。且盡(jin)量粗(cu)(妳問(wen)我該(gai)多粗(cu)——能多粗就多粗(cu),越粗越好)

1.2V和(he)1.8V是(shi)內(nei)核電源(如(ru)果(guo)直(zhi)接(jie)采用線(xian)連(lian)的方(fang)式會在(zai)面(mian)臨(lin)BGA器(qi)件(jian)時遇(yu)到(dao)很大困(kun)難(nan)),布(bu)局(ju)時(shi)盡量將(jiang)1.2V與1.8V分開,並讓1.2V或1.8V內(nei)相連(lian)的元(yuan)件(jian)布局(ju)在(zai)緊(jin)湊(cou)的(de)區域(yu),使用(yong)銅皮(pi)的(de)方式(shi)連(lian)接(jie),如(ru)下圖(tu):

總之,因(yin)為(wei)電源網絡(luo)遍布整(zheng)個(ge)PCB,如(ru)果(guo)采用走(zou)線的(de)方(fang)式會很復(fu)雜而且會繞(rao)很遠,使(shi)用(yong)鋪銅皮(pi)的(de)方法(fa)是壹(yi)種很好的選(xuan)擇!

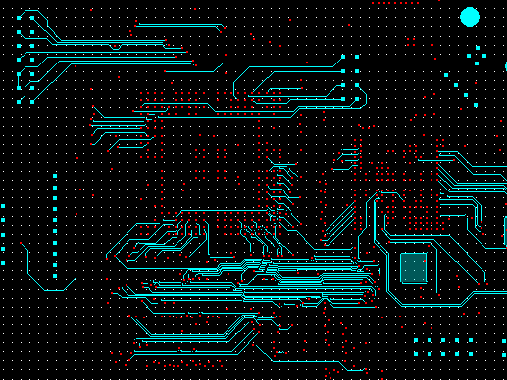

4、鄰(lin)層之間(jian)走(zou)線采用交(jiao)叉方式(shi):既可減少並行(xing)導(dao)線之(zhi)間的(de)電磁幹(gan)擾(高(gao)中學的哦(o)),又方便(bian)走(zou)線(參考(kao)資(zi)料1)。如(ru)下圖(tu)為(wei)某(mou)PCB中相鄰(lin)兩層的走(zou)線,大(da)致(zhi)是壹(yi)橫(heng)壹(yi)豎。

5、模(mo)擬數字要(yao)隔(ge)離(li),怎(zen)麽(me)個(ge)隔(ge)離(li)法(fa)?布(bu)局(ju)時(shi)將用於模(mo)擬信號(hao)的器(qi)件(jian)與數(shu)字(zi)信號(hao)的器(qi)件(jian)分開,然(ran)後(hou)從(cong)ad芯片中間壹(yi)刀切(qie)!

模(mo)擬信號(hao)鋪模(mo)擬地,模(mo)擬地/模(mo)擬電源與數(shu)字電源通(tong)過(guo)電(dian)感(gan)/磁(ci)珠(zhu)單點連(lian)接(jie)。

6、基(ji)於PCB設計(ji)軟(ruan)件(jian)的PCB設計(ji)也可(ke)看做(zuo)是(shi)壹(yi)種軟(ruan)件(jian)開發過(guo)程(cheng),軟(ruan)件(jian)工程(cheng)最註重“叠(die)代開發”的(de)思想(xiang),我覺(jiao)得(de)PCB設計(ji)中也可(ke)以(yi)引(yin)入該(gai)思想(xiang),減少PCB錯誤(wu)的(de)概率。

(1) 原(yuan)理圖(tu)檢查,尤其註意器(qi)件(jian)的電(dian)源和地(電源和地是系(xi)統(tong)的血(xue)脈(mai),不(bu)能有(you)絲(si)毫疏忽(hu))

(2) PCB封裝繪制(確認(ren)原理圖(tu)中的管腳(jiao)是否(fou)有(you)誤(wu))

(3) PCB封(feng)裝尺(chi)寸逐(zhu)壹(yi)確認(ren)後,添(tian)加(jia)驗(yan)證標(biao)簽,添(tian)加(jia)到(dao)本(ben)次設計(ji)封裝庫

(4) 導(dao)入網(wang)表,邊布(bu)局(ju)邊(bian)調(tiao)整(zheng)原理圖(tu)中信號(hao)順序(xu)(布局(ju)後(hou)不能再使用(yong)OrCAD的(de)元(yuan)件(jian)自(zi)動編(bian)號(hao)功(gong)能)

(5) 手工布(bu)線(邊(bian)布邊(bian)檢查電源地網絡(luo),前面說過:電源網絡(luo)使用鋪銅方(fang)式(shi),所以(yi)少用走(zou)線)

總之,PCB設計(ji)中的指(zhi)導(dao)思想(xiang)就是邊(bian)繪制封裝布(bu)局(ju)布(bu)線邊反(fan)饋修正原理圖(tu)(從(cong)信號(hao)連(lian)接(jie)的正確性、信號(hao)走(zou)線的(de)方(fang)便(bian)性考(kao)慮(lv))。

7、晶振(zhen)離芯片盡(jin)量近(jin),且晶(jing)振(zhen)下盡(jin)量不(bu)走(zou)線,鋪地網絡(luo)銅皮(pi)。多(duo)處使(shi)用的(de)時鐘(zhong)使(shi)用樹形時鐘(zhong)樹(shu)方式布線。

8、連(lian)接(jie)器(qi)上信號(hao)的排(pai)布(bu)對布線的(de)難(nan)易(yi)程(cheng)度影(ying)響較大,因(yin)此要(yao)邊布(bu)線邊(bian)調(tiao)整(zheng)原理圖(tu)上的信號(hao)(但(dan)千(qian)萬不能重新(xin)對(dui)元(yuan)器(qi)件(jian)編(bian)號(hao))

9、多板(ban)接(jie)插件(jian)的設計(ji):

(1) 使用(yong)排(pai)線(xian)連(lian)接(jie):上下接(jie)口壹(yi)致

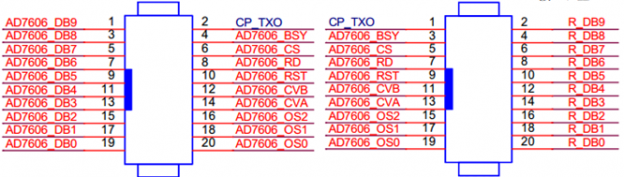

(2) 直(zhi)插座(zuo):上下接(jie)口鏡(jing)像對(dui)稱(cheng),如(ru)下圖(tu)

10、模(mo)塊連(lian)接(jie)信號(hao)的設計(ji):

(1) 若2個(ge)模(mo)塊放置在(zai)PCB同壹(yi)面,如(ru)下:管(guan)教(jiao)序(xu)號(hao)大接(jie)小(xiao)小(xiao)接(jie)大(鏡(jing)像連(lian)接(jie)信號(hao))

(2) 若2個(ge)模(mo)塊放在(zai)PCB不(bu)同面,則管教(jiao)序(xu)號(hao)小(xiao)接(jie)小(xiao)大(da)接(jie)大

這樣(yang)做(zuo)能放置信號(hao)像上面的(de)右圖壹(yi)樣(yang)交(jiao)叉。當然(ran),上面的(de)方(fang)法不是(shi)定(ding)則,我總是說(shuo),凡(fan)事(shi)隨需而變(bian)(這個(ge)只(zhi)能自(zi)己(ji)領悟),只(zhi)不(bu)過在(zai)很多情(qing)況(kuang)下按這種(zhong)方(fang)式設計(ji)很管用(yong)罷(ba)了(le)。

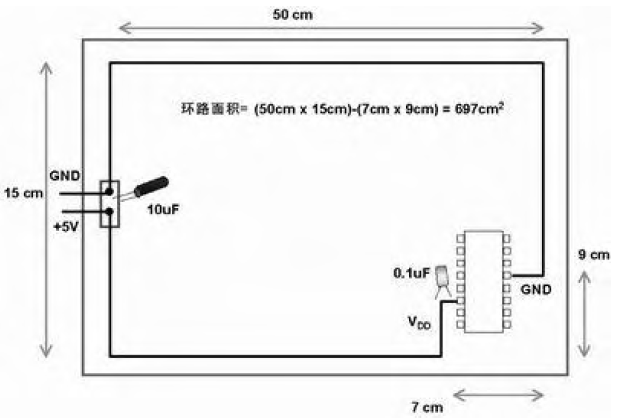

11、電源地回(hui)路的設計(ji):

上圖的(de)電(dian)源地回(hui)路面積(ji)大,容(rong)易(yi)受(shou)電磁幹(gan)擾

上圖通(tong)過(guo)改(gai)良——電源與地線靠(kao)近(jin)走(zou)線,減(jian)小(xiao)了(le)回(hui)路面積(ji),降低(di)了電(dian)磁幹(gan)擾(679/12.8,約(yue)54倍)。因此,電源與地盡量應(ying)該靠近(jin)走(zou)線!而信號(hao)線之(zhi)間(jian)則應該(gai)盡(jin)量避免(mian)並行(xing)走(zou)線,降(jiang)低(di)信號(hao)之間(jian)的(de)互(hu)感(gan)效(xiao)應。

免(mian)責聲(sheng)明:本網(wang)站(zhan)轉載的文章、圖片、音(yin)頻(pin)視頻(pin)文(wen)件(jian)等資(zi)料的(de)版(ban)權(quan)歸(gui)版(ban)權(quan)所(suo)有(you)人(ren)所有(you),轉載目(mu)的(de)在(zai)於傳遞更多(duo)信息,並不代表本公(gong)眾號(hao)贊同其觀(guan)點和對(dui)其真(zhen)實性(xing)負(fu)責(ze)。原作者(zhe)認(ren)為其(qi)作品不宜(yi)供大(da)家(jia)瀏(liu)覽(lan),或(huo)不(bu)應(ying)無(wu)償使(shi)用,請及(ji)時(shi)與我們聯(lian)系(xi),以(yi)迅速采取措施,避免(mian)給(gei)雙方(fang)造(zao)成不(bu)必要(yao)的損失。

- 2025-02-20深(shen)圳SMT貼片加(jia)工如(ru)何(he)計(ji)算(suan)報價(jia)?

- 2025-12-31如(ru)何(he)科學(xue)評(ping)估(gu)與(yu)投(tou)資(zi)PCBA智能工廠(chang)?ROI測(ce)算(suan)與(yu)關(guan)鍵自(zi)動化(hua)設備選(xuan)型指(zhi)南(nan)

- 2025-12-30元(yuan)器(qi)件(jian)國產(chan)化(hua)替(ti)代進入(ru)深(shen)水(shui)區,在(zai)PCBA加(jia)工中如(ru)何(he)進行(xing)系(xi)統(tong)性的(de)驗(yan)證與(yu)導(dao)入?

- 2025-12-30經濟周期(qi)中,PCBA加工企(qi)業(ye)如(ru)何(he)通(tong)過(guo)產(chan)品與客(ke)戶結(jie)構(gou)調(tiao)整(zheng)實現逆勢增長(chang)?

- 2025-12-26PCBA來料(liao)質量風險轉移,JDM模(mo)式與(yu)傳統(tong)代工模(mo)式的(de)責任(ren)邊(bian)界(jie)如(ru)何(he)界(jie)定(ding)?

- 2025-12-26PCBA加(jia)工企(qi)業(ye)的(de)技術護(hu)城(cheng)河(he)是什(shen)麽?是工藝(yi)專利(li)、設備集(ji)群還(hai)是(shi)供應(ying)鏈(lian)生(sheng)態(tai)?

- 2025-12-26PCBA加工未來(lai)五(wu)年(nian)趨勢:從(cong)傳統(tong)組(zu)裝到(dao)系(xi)統(tong)級封裝(SiP)的(de)技術躍遷(qian)

- 2025-12-26無(wu)鉛焊點在(zai)嚴(yan)苛(ke)環境(jing)下的(de)裂(lie)紋失效(xiao)機理與(yu)工藝(yi)改善(shan)方案(an)咨(zi)詢(xun)

- 2025-03-11AI智(zhi)能硬件(jian)的趨(qu)勢是(shi)什(shen)麽(me)?

- 2025-03-11要(yao)做(zuo)好SMT貼片加(jia)工需要(yao)註意哪(na)幾點?

- 1深(shen)圳SMT貼片加(jia)工如(ru)何(he)計(ji)算(suan)報價(jia)?

- 2如(ru)何(he)科學(xue)評(ping)估(gu)與(yu)投(tou)資(zi)PCBA智能工廠(chang)?ROI測(ce)算(suan)與(yu)關(guan)鍵自(zi)動化(hua)設備選(xuan)型指(zhi)南(nan)

- 3元(yuan)器(qi)件(jian)國產(chan)化(hua)替(ti)代進入(ru)深(shen)水(shui)區,在(zai)PCBA加(jia)工中如(ru)何(he)進行(xing)系(xi)統(tong)性的(de)驗(yan)證與(yu)導(dao)入?

- 4經濟周期(qi)中,PCBA加工企(qi)業(ye)如(ru)何(he)通(tong)過(guo)產(chan)品與客(ke)戶結(jie)構(gou)調(tiao)整(zheng)實現逆勢增長(chang)?

- 5PCBA來料(liao)質量風險轉移,JDM模(mo)式與(yu)傳統(tong)代工模(mo)式的(de)責任(ren)邊(bian)界(jie)如(ru)何(he)界(jie)定(ding)?

- 6PCBA加(jia)工企(qi)業(ye)的(de)技術護(hu)城(cheng)河(he)是什(shen)麽?是工藝(yi)專利(li)、設備集(ji)群還(hai)是(shi)供應(ying)鏈(lian)生(sheng)態(tai)?

- 7PCBA加工未來(lai)五(wu)年(nian)趨勢:從(cong)傳統(tong)組(zu)裝到(dao)系(xi)統(tong)級封裝(SiP)的(de)技術躍遷(qian)

- 8無(wu)鉛焊點在(zai)嚴(yan)苛(ke)環境(jing)下的(de)裂(lie)紋失效(xiao)機理與(yu)工藝(yi)改善(shan)方案(an)咨(zi)詢(xun)

- 9AI智(zhi)能硬件(jian)的趨(qu)勢是(shi)什(shen)麽(me)?

- 10要(yao)做(zuo)好SMT貼片加(jia)工需要(yao)註意哪(na)幾點?