PCB中的(de)微(wei)帶線和(he)帶狀線有什(shen)麽(me)區別(bie)?

- 發表(biao)時間:2021-06-22 16:00:34

- 來源:本(ben)站(zhan)

- 人(ren)氣(qi):1652

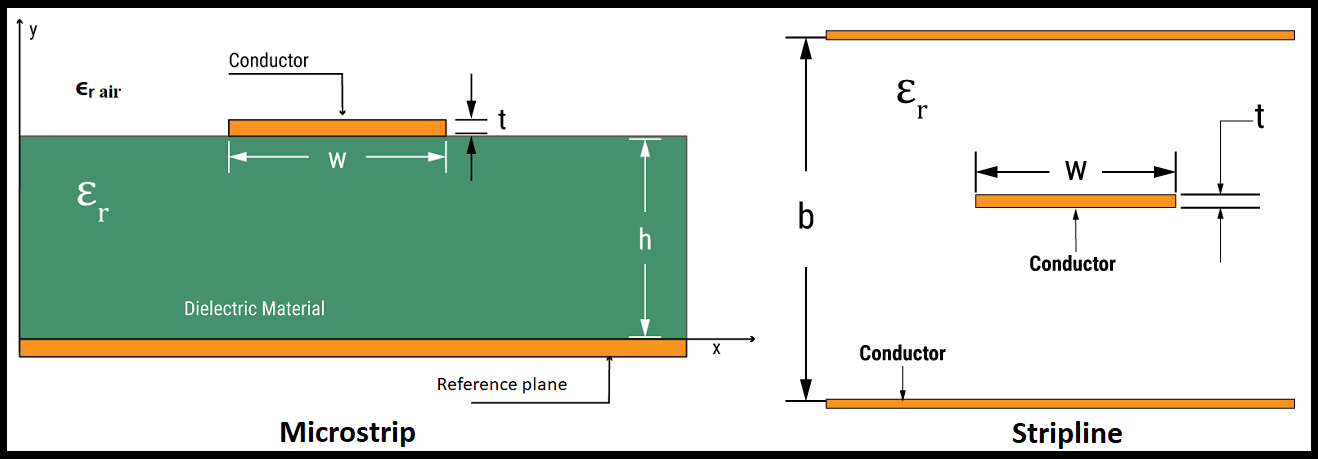

PCB 通常使用(yong)兩(liang)種類(lei)型的(de)傳輸(shu)線:微帶線和(he)帶狀線。每(mei)條(tiao)傳(chuan)輸(shu)線都(dou)由(you)信號走線和(he)參考(kao)平(ping)面組成。根(gen)據傳輸線幾何形(xing)狀,必須將(jiang)信號走線和(he)參考(kao)平(ping)面視(shi)為(wei)壹(yi)個單元。並(bing)且永遠(yuan)不(bu)要(yao)將(jiang)它(ta)們分開,因(yin)為微帶線和(he)帶狀線具(ju)有定(ding)義(yi)其(qi)特性(xing)的獨(du)特 EM 場分布。

通過(guo)將 PCB 走(zou)線阻抗與信(xin)號源匹(pi)配(pei),可以(yi)避免PCB 傳輸(shu)線中的(de)信(xin)號反(fan)射(she)。但了(le)解哪種(zhong)阻抗匹(pi)配(pei)技(ji)術(shu)適(shi)用(yong)於設計也(ye)很(hen)重(zhong)要。我(wo)必須告訴妳(ni),沒(mei)有壹(yi)種(zhong)傳輸線技(ji)術(shu)是(shi)完美(mei)的(de)。涉(she)及(ji)傳(chuan)輸線的PCB 設計方(fang)程只是(shi)近(jin)似(si)值(zhi),根(gen)據規格(ge)有不(bu)同程度的精確度。

微帶線和(he)帶狀線傳輸線的電磁(ci)場分布可以(yi)通過(guo)選擇PCB 材料(liao)(介(jie)電常數和(he)損(sun)耗(hao)角(jiao)正切)和(he)調整(zheng)引導波(bo)長(chang)、傳播(bo)速度和(he)特性(xing)阻抗來改(gai)變。這(zhe)些參數(shu)最(zui)終(zhong)會改(gai)變電磁(ci)場分布,從而(er)改(gai)變傳(chuan)輸(shu)線的特性。

PCB中的(de)微(wei)帶線是什麽?

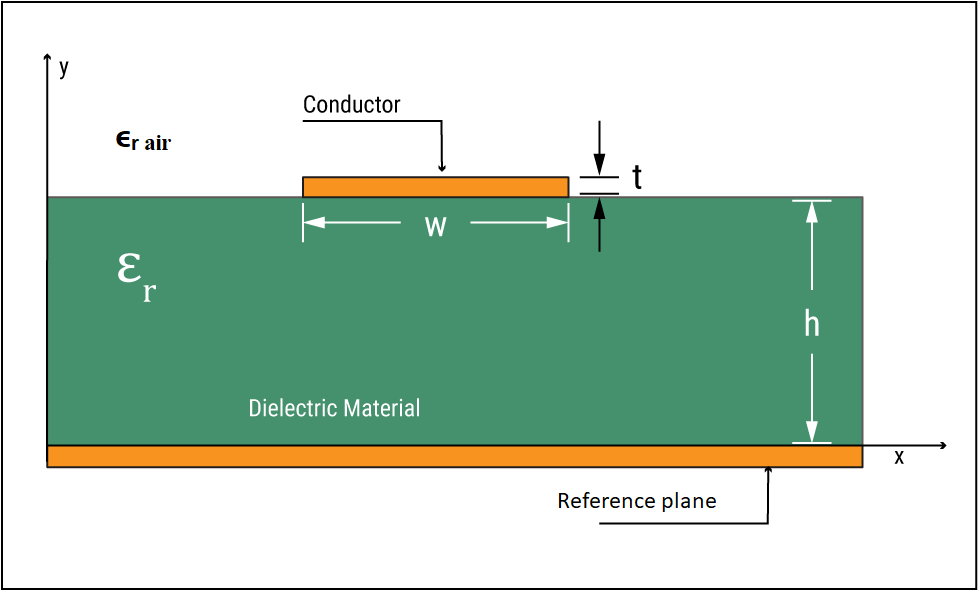

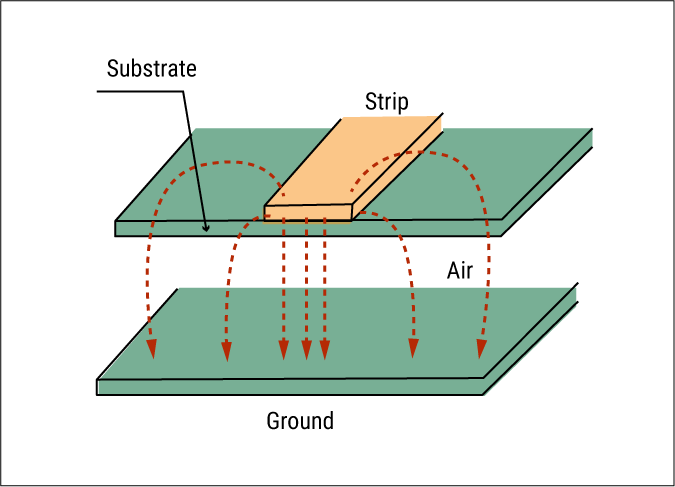

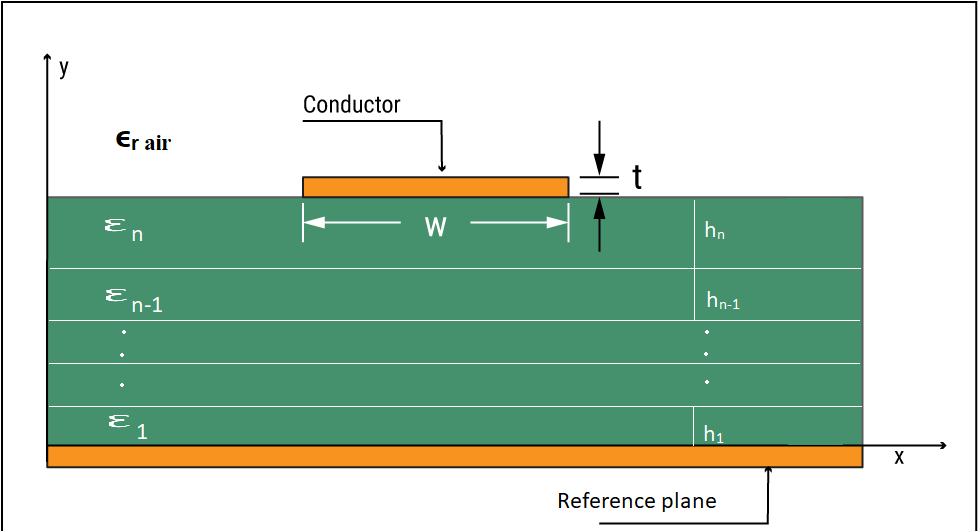

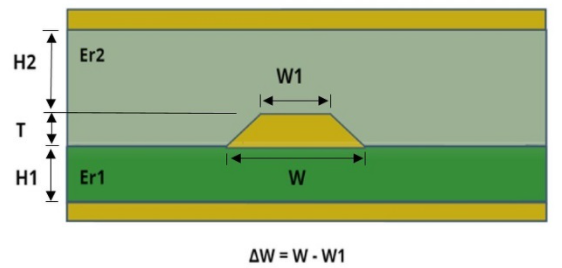

微帶由(you)位(wei)於由(you)接地(di)平(ping)面支持的介(jie)電基(ji)板(ban)上的(de)條狀導體組(zu)成。

微(wei)帶(dai)線是壹(yi)種(zhong)平(ping)面傳輸(shu)線,主要用(yong)於射頻(pin)和(he)微波(bo)電路。它(ta)在(zai)PCB表(biao)面(mian)布線,周圍(wei)有兩(liang)種(zhong)環(huan)境(jing):PCB材料(liao)和(he)空氣(qi)。微帶(dai)由(you)位(wei)於介(jie)電基(ji)板(ban)上的(de)條狀導體(焊盤)組成,該(gai)基(ji)板由(you)接地(di)平(ping)面支持,當(dang)接地(di)平(ping)面和(he)條帶(dai)之間的間距增(zeng)加時,該(gai)接地(di)平(ping)面會輻射(she)。

微(wei)帶(dai)線中的(de)傳(chuan)播方(fang)式是(shi)什麽(me)?

在(zai)微帶(dai)中,主要的傳(chuan)播模(mo)式(shi)是準(zhun) TEM(橫向電磁(ci))。因(yin)此,截面中的(de)相(xiang)速度、特性阻抗和(he)場變化(hua)變得與頻(pin)率相(xiang)關。

微帶中傳(chuan)播(bo)的電磁(ci)場。

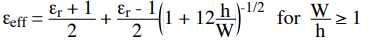

微帶(dai)中的(de)有效(xiao)介(jie)電常數 (ϵ eff ) 是(shi)多(duo)少(shao)?

存(cun)儲(chu)在(zai)微帶(dai)排列中的(de)電能(neng)存(cun)在(zai)於空氣(qi)和(he)電介(jie)質中,因(yin)此(ci)傳輸(shu)線上信號的有效(xiao)介(jie)電常數將(jiang)介(jie)於空氣(qi)和(he)電介(jie)質的(de)介(jie)電常數之(zhi)間。該(gai)有效(xiao)介(jie)電常數決(jue)定(ding)了(le)微(wei)帶傳(chuan)輸(shu)線上電磁(ci)波(bo)的相(xiang)速度。

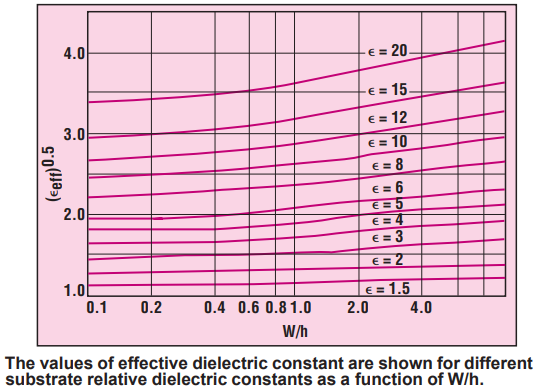

微帶線是分散的(de)。隨著(zhe)頻(pin)率的(de)增(zeng)加,有效(xiao)介(jie)電常數也(ye)向基板方(fang)向增(zeng)加,導致相速(su)度降(jiang)低。有效(xiao)介(jie)電常數考(kao)慮(lv)到大部(bu)分(fen)電場保留在(zai)基板(ban)內(nei),但總能(neng)量的某(mou)壹(yi)部(bu)分存(cun)在(zai)於電路板(ban)上(shang)方(fang)的空氣(qi)中。

ϵ eff也隨自由(you)空間波(bo)長(chang)而變化(hua)。隨(sui)著(zhe)帶材寬(kuan)度與基材厚(hou)度/寬度/高(gao)度的比(bi)率(lv)減小(xiao),這(zhe)種分散變得更加顯著(zhe)。隨著(zhe)帶鋼(gang)寬度的增(zeng)加,色(se)散不(bu)那麽明(ming)顯(xian)。在(zai)這種(zhong)情況(kuang)下(xia),微帶(dai)線似(si)乎(hu)是(shi)壹(yi)個理(li)想(xiang)的平(ping)行板電容器。ϵ eff應大於空氣(qi)的介(jie)電常數 ( ϵ r = 1) 並(bing)小(xiao)於基板(ban)的介(jie)電常數。閱讀(du)PCB 基板(ban):了(le)解介(jie)電材料(liao)的(de)特(te)性(xing)。

圖(tu)片來源:Leo G. Maloratsky 回(hui)顧微(wei)帶(dai)線的基礎知(zhi)識。

挑(tiao)戰在(zai)於導體條(tiao)不(bu)能(neng)浸(jin)入單個電介(jie)質中

與(yu)微(wei)帶參數(shu)計算(suan)相關的具(ju)有挑(tiao)戰性的問題(ti)是(shi)導體帶(dai)未(wei)浸(jin)入(ru)單壹(yi)介(jie)電材料(liao)中。壹(yi)方(fang)面,它(ta)是電介(jie)質,另(ling)壹(yi)方(fang)面,它(ta)通常是空氣(qi)。有效(xiao)介(jie)電常數的(de)概念是(shi)專(zhuan)門為應對(dui)這壹(yi)挑(tiao)戰而開發的。所(suo)述(shu) εeff 表(biao)示(shi)板材料(liao)(相(xiang)對(dui)介(jie)電常數之(zhi)間的壹(yi)些中間值(zhi)率(lv)εr)和(he)空氣(qi)(相當(dang)於1)。因此(ci),這可用(yong)於計算(suan)微帶參數(shu)。

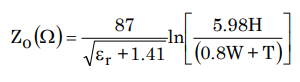

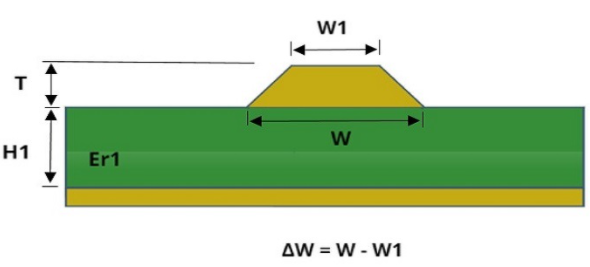

微帶(dai)線的特性阻抗

對(dui)於給定(ding)的(de) PCB 層壓(ya)板(ban)和(he)銅(tong)重(zhong)量,信號走線的寬度 (W) 除外(wai),下(xia)面給(gei)出的(de)公式可用(yong)於設計 PCB 走(zou)線以匹(pi)配(pei)電路所(suo)需的(de)阻抗。對(dui)於寬度為 W 和(he)厚度為 T 的信號走線,通過(guo)具(ju)有介(jie)電常數ϵr的(de) PCB 電介(jie)質與(yu)接地(di)(或(huo)電源)平(ping)面相距距離 H ,其(qi)特征(zheng)阻抗 (Zo) 為:

微帶線的特性阻抗隨著(zhe)頻(pin)率的(de)增(zeng)加而(er)變化(hua)。這(zhe)裏(li)值(zhi)得註意的壹(yi)點(dian)是(shi),IPC 微(wei)帶(dai)線方(fang)程在(zai) 50 到 100Ω 之間最(zui)準(zhun)確(que),但對(dui)於較低/較(jiao)高(gao)阻抗則不太(tai)準(zhun)確。

註意:所(suo)有尺(chi)寸均(jun)以密耳(er)為單位(wei)。

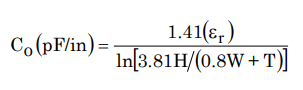

微帶(dai)線的特征電容

其(qi)中 T 是(shi)電路板(ban)厚(hou)度,H 是走線之間的間距。

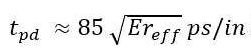

微(wei)帶(dai)線延(yan)遲(chi)常數

對(dui)於給定(ding)的(de)傳輸(shu)線幾何形(xing)狀,延(yan)遲(chi)常數僅(jin)是(shi)介(jie)電常數的(de)函數(shu),而(er)不(bu)是跡(ji)線尺(chi)寸的函數(shu)。對(dui)於給定(ding)的(de) PCB 層壓(ya)板(ban)和(he)介(jie)電常數,各(ge)種(zhong)阻抗線的傳播延(yan)遲(chi)常數是(shi)固定(ding)的(de)。

微帶結(jie)構(gou)的優(you)點(dian)

微(wei)帶(dai)線是壹(yi)種(zhong)“開放”的(de)線結(jie)構(gou);它使連接組件(jian)變得非(fei)常容易。

它(ta)可以(yi)以最(zui)小(xiao)串擾(rao)的(de)高(gao)密度(多(duo)通道)封(feng)裝在(zai)壹(yi)起(qi),使其(qi)適用(yong)於射頻(pin)和(he)微波(bo) IC 設計。

它(ta)的平(ping)面拓撲結(jie)構(gou)受PCB 制造(zao)工(gong)藝公差(cha)的(de)影響最(zui)小(xiao)。

它(ta)具(ju)有更(geng)快(kuai)的傳(chuan)播時間。

這種(zhong)技(ji)術(shu)同時提(ti)供(gong)了(le)良(liang)好的(de)散熱和(he)機械(xie)支持。閱讀(du)12 種減(jian)少(shao) PCB 發熱的(de) PCB 熱管理(li)技(ji)術(shu)。

微(wei)帶(dai)線損(sun)耗(hao)

線路導體的(de)有限(xian)電導率

輻射(she)效(xiao)應(取決(jue)於介(jie)電常數、基(ji)板厚(hou)度、電路幾何形(xing)狀和(he)頻(pin)率)

與(yu)磁(ci)性(xing)基板相(xiang)關的磁(ci)損(sun)耗(hao),如鐵氧體

襯(chen)底(di)的有限(xian)電阻率和(he)傾倒(dao)現象(xiang)

註意:盡(jin)管微帶線具(ju)有低成本(ben)和(he)緊湊(cou)尺(chi)寸的優(you)勢,但它(ta)比(bi)同軸線、波(bo)導、CPW 和(he)帶狀線的損(sun)耗(hao)更大(da)。

如何減少(shao)微帶(dai)線的損(sun)耗(hao)?

將基板懸浮(fu)在(zai)空氣(qi)上以(yi)減少(shao)微帶(dai)線的損(sun)耗(hao)。

它可以(yi)通過(guo)將基(ji)材懸浮(fu)在(zai)空氣(qi)中來完成。微(wei)帶(dai)的懸掛(gua)意味著(zhe)信號和(he)接地(di)路徑(jing)之(zhi)間的間隔增(zeng)加,這(zhe)也增(zeng)強(qiang)了(le)微(wei)帶輻射(she)的(de)趨(qu)勢,特別(bie)是在(zai)不連(lian)續(xu)處(chu)。

懸浮(fu)如何幫助(zhu)減少(shao)微帶(dai)線的損(sun)耗(hao)?

基板(ban)底(di)部和(he)地(di)平(ping)面之間的空氣(qi)包含(han)電磁(ci)場。微帶(dai)線的插(cha)入損(sun)耗(hao)降(jiang)低,因(yin)為(wei)與(yu)標準電路板(ban)基(ji)板相比(bi),空氣(qi)基本(ben)上(shang)沒(mei)有介(jie)電損(sun)耗(hao)。此外(wai),由(you)於較低的(de)有效(xiao)介(jie)電常數,微(wei)帶線的寬度增(zeng)加。較(jiao)寬的線路具(ju)有較(jiao)低的(de)電流(liu)密(mi)度,因此具(ju)有較(jiao)低的(de)歐姆損(sun)耗(hao)。微帶(dai)懸浮(fu)技(ji)術(shu)僅(jin)用(yong)於幾GHz。

註意: 較小(xiao)的(de)寬度總是(shi)會導致更多(duo)的損(sun)失。

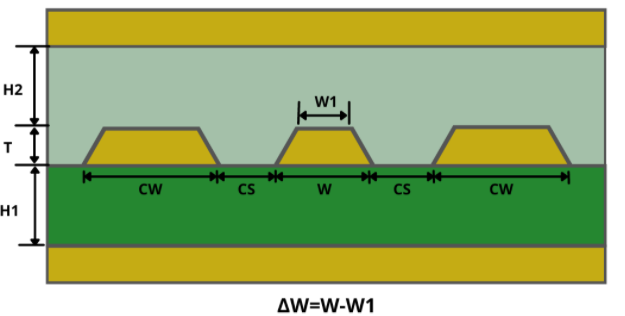

多(duo)層微(wei)帶線

微帶幾何用(yong)於在(zai)低頻(pin)下(xia)傳導 EM 波(bo),但超過(guo) 60GHz,由(you)於損(sun)耗(hao),其(qi)應用(yong)受(shou)到限制(zhi)。這(zhe)就是(shi)它(ta)們不(bu)能(neng)在(zai)太(tai)赫(he)茲頻(pin)率下(xia)使用(yong)的(de)原因(yin)。

在(zai)多(duo)層微(wei)帶中使(shi)用(yong)不(bu)同的襯底(di)層。

可以(yi)在(zai)不同配(pei)置的(de)襯底(di)層上(shang)設計多(duo)層微(wei)帶線。它可以(yi)是單層、雙層(ceng)或(huo)多(duo)層材料(liao)。隨(sui)著(zhe)SoC要求(qiu)的需(xu)要(yao),在(zai)高(gao)頻(pin)下(xia)多(duo)層基(ji)板的使用(yong)有所(suo)增(zeng)加。

多(duo)層基(ji)板材料(liao)在(zai)微帶(dai)建設中的(de)優(you)勢

減少(shao)損(sun)失和(he)控(kong)制(zhi)膨脹系(xi)數(shu)

適用(yong)於天線設計,提(ti)供良(liang)好的(de)表(biao)面(mian)波(bo)抗擾(rao)增(zeng)益和(he)帶寬(kuan)增(zeng)強(qiang)以(yi)及(ji)良(liang)好的(de)機械(xie)集成

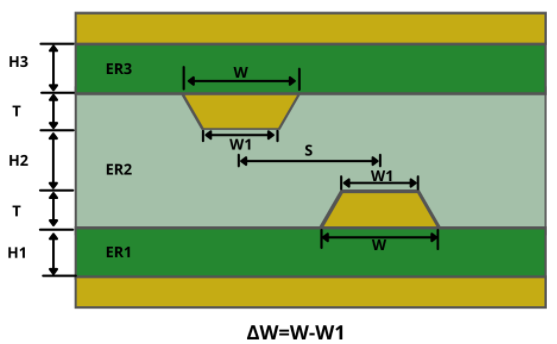

PCB中的(de)帶(dai)狀線是什麽?

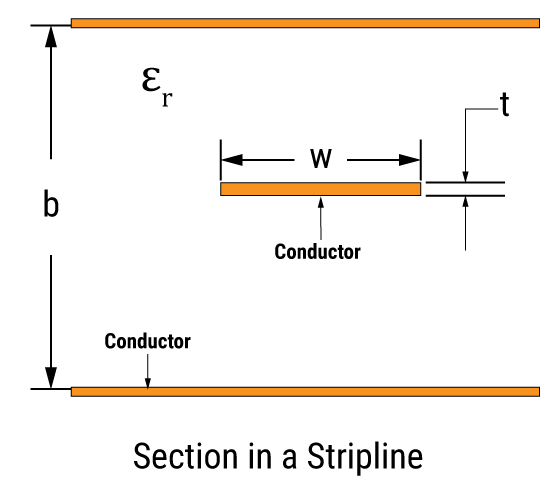

帶狀線布線在(zai) PCB 的內(nei)層(ceng),這(zhe)就是(shi)為(wei)什麽(me)它只被(bei)壹(yi)種(zhong)環(huan)境(jing)包(bao)圍(wei),即(ji) PCB 材料(liao)。這(zhe)種(zhong)技(ji)術(shu)最(zui)好(hao)用(yong)於多(duo)層 PCB 設計,信(xin)號走線由(you)上下(xia)的接地(di)層(ceng)支撐。

在(zai)帶狀線中,高(gao)頻(pin)信號走線的電流(liu)返(fan)回(hui)路徑(jing)位(wei)於接地(di)(電源)平(ping)面上的(de)信(xin)號走線上方(fang)和(he)下(xia)方(fang)。由(you)於這種(zhong)安排,高(gao)頻(pin)信號保留在(zai) PCB 內(nei)部(bu),從(cong)而減(jian)少(shao)了(le)輻射(she),並(bing)提(ti)供(gong)了(le)對(dui)傳入(ru)雜(za)散信(xin)號的屏蔽。

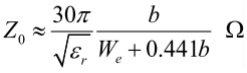

帶狀線的特性阻抗

帶狀線的特性阻抗取決(jue)於介(jie)電常數以(yi)及(ji)帶(dai)狀中心(xin)導體和(he)接地(di)平(ping)面的橫截面幾何形(xing)狀。帶狀線的特征阻抗隨著(zhe)帶寬(kuan)度W e 的增(zeng)加而(er)減小(xiao)。

註: b 為兩平(ping)面間距,W e為(wei)有效(xiao)帶(dai)鋼(gang)寬(kuan)度。

帶狀線的特征電容

帶狀線延(yan)遲(chi)常數

帶(dai)狀線中給(gei)定(ding)長(chang)度的傳播延(yan)遲(chi) (tpd) 只(zhi)是(shi)電介(jie)質 εr 的(de)函數(shu)。

帶狀線設計註(zhu)意事(shi)項(xiang)

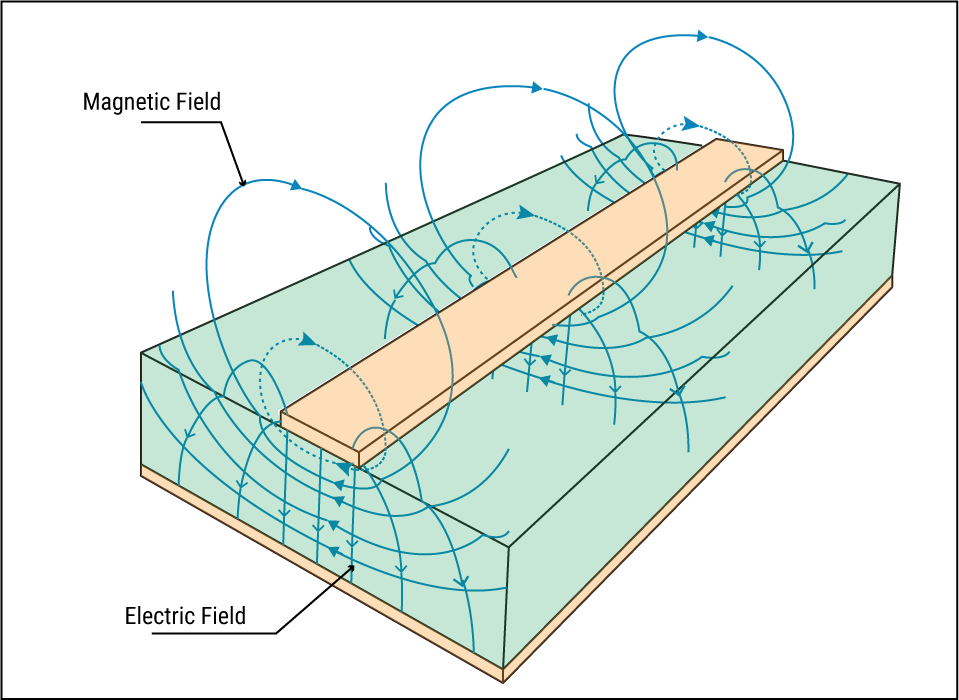

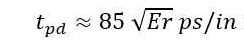

帶狀線中的(de)電磁(ci)場分布。

帶狀線傳輸線由(you)三層(ceng)導體組(zu)成,其(qi)中內(nei)部(bu)導體稱為“夾層(ceng)導體”,而(er)連(lian)接在(zai)信號地(di)的(de)另(ling)外(wai)兩個導體稱為接地(di)導體。夾層(ceng)導體嵌入(ru)均(jun)勻且各(ge)向同性的電介(jie)質中,具(ju)有介(jie)電常數 (Er)。

帶(dai)狀線中基(ji)本(ben) TEM 模(mo)式(shi)的(de)電“E”和(he)磁“H”場線在(zai)上面(mian)以定(ding)義(yi)的橫截面和(he)定(ding)義(yi)的時間表(biao)示(shi)。

帶狀線外(wai)導體之(zhi)間的區(qu)域(yu)僅(jin)包(bao)含(han)單壹(yi)介(jie)質。這(zhe)就是(shi)基(ji)模 (TEM) 的(de)相速度和(he)特征(zheng)阻抗不隨(sui)頻(pin)率變化(hua)的(de)原因(yin)。

在(zai) TEM 模式(shi)下(xia),內(nei)導體處(chu)於等電位(wei)(每(mei)個點(dian)都(dou)處(chu)於相同電位(wei))。

帶狀線布置的(de)優(you)點(dian)

它(ta)為(wei)信(xin)號走線提供屏蔽和(he)保護(hu)。

低阻抗,因此(ci)更(geng)少(shao)的輻射(she)和(he)串擾(rao)

50MHz以(yi)上(shang)可見改(gai)善(shan)

帶狀線排列具(ju)有更(geng)好(hao)的 EMI 特(te)性。

帶狀線排列的局(ju)限(xian)性

由(you)於帶狀線包含嵌入(ru)式(shi)信號走線,因此很(hen)難(nan)調試(shi)此(ci)類(lei)走(zou)線。換句(ju)話說,PCB 原(yuan)型設計和(he)故障(zhang)排除(chu)會很(hen)困(kun)難(nan)。

解耦難(nan)

低阻抗以實(shi)現正(zheng)確(que)匹(pi)配(pei)

帶狀線的損(sun)耗(hao)是多(duo)少(shao)?

其(qi)導體的(de)有限(xian)電導率

磁共(gong)振(zhen)

電介(jie)質的(de)有限(xian)電阻率和(he)傾倒(dao)現象(xiang)

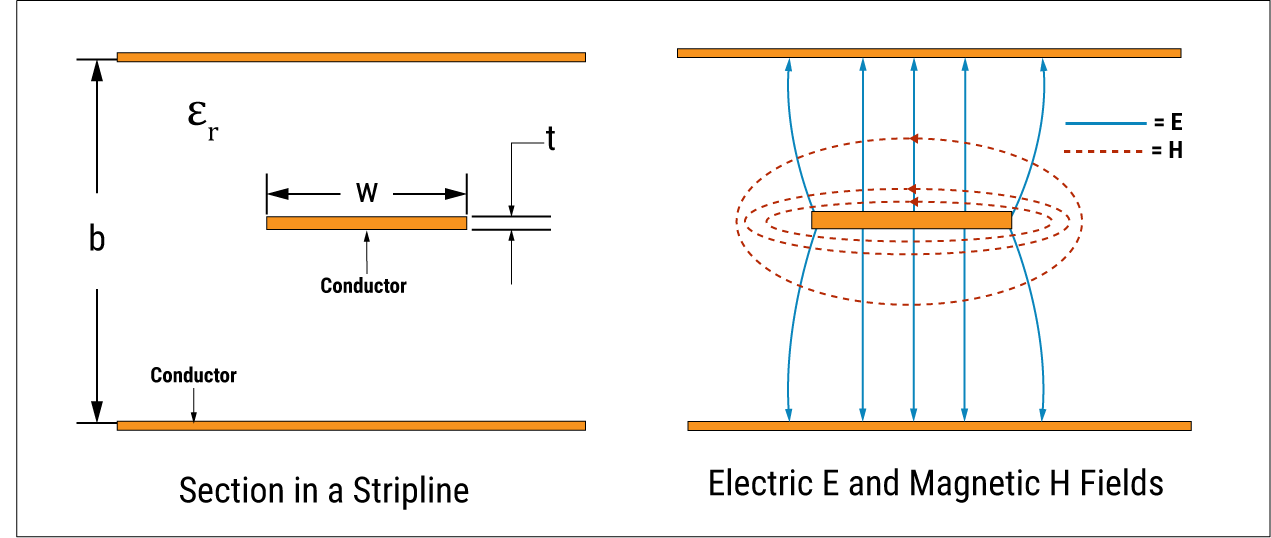

設計具(ju)有帶(dai)狀線幾何形(xing)狀的多(duo)層板(ban)

多(duo)層電路板(ban)通常需要(yao)帶狀線,因為它可以(yi)在(zai)層之(zhi)間布線,但帶(dai)狀線的接地(di)需(xu)要(yao)適(shi)當(dang)註(zhu)意。如果頂部(bu)和(he)底(di)部接地(di)層(ceng)的(de)電位(wei)不同,則平(ping)行板模(mo)式可以(yi)在(zai)它們(men)之間傳播(bo)。如果激(ji)發,這種模(mo)式(shi)將不(bu)會局限於帶附(fu)近的(de)區(qu)域,而是能(neng)夠(gou)傳(chuan)播到存(cun)在(zai)兩個接地(di)平(ping)面的任(ren)何(he)地(di)方(fang)。

帶狀線比(bi)微(wei)帶線對(dui)金屬外(wai)殼的橫向接地(di)平(ping)面更不(bu)敏(min)感,因(yin)為電磁(ci)場在(zai)中心(xin)導體和(he)上下(xia)接地(di)平(ping)面附近(jin)被(bei)強(qiang)烈(lie)包(bao)含。

如果頂部(bu)和(he)底(di)部地(di)平(ping)面的電位(wei)不同,會發生什麽(me)?

帶狀線中的(de)頂(ding)部和(he)底(di)部地(di)平(ping)面。

平(ping)行板模(mo)式將(jiang)開(kai)始(shi)在(zai)頂面(mian)和(he)地(di)平(ping)面之間傳播(bo)。並(bing)且它(ta)不(bu)會局限於條帶(dai)周圍(wei)的(de)區域(yu),而(er)是(shi)會在(zai)存(cun)在(zai)兩個接地(di)平(ping)面的任(ren)何(he)地(di)方(fang)傳播(bo)。平(ping)行板模(mo)式可以(yi)通過(guo)以下(xia)方(fang)式抑(yi)制:

使(shi)用(yong)金(jin)屬化通孔連接頂部(bu)和(he)底(di)部地(di)平(ping)面

緊密(mi)放置過(guo)孔(過(guo)孔之間的間距應為電介(jie)質中波(bo)長(chang)的 1/8,以(yi)防止(zhi)接地(di)層(ceng)之(zhi)間的電位(wei)差(cha)。)

如果過(guo)孔放置得太(tai)靠(kao)近(jin)帶(dai)狀線邊緣,它們(men)可能(neng)會幹擾(rao)特(te)性(xing)阻抗。因此(ci),過(guo)孔間距應至少(shao)為 3 條(tiao)帶寬度。

那麽,是否有可能(neng)在(zai)不使(shi)用(yong)帶(dai)狀線排列的情(qing)況(kuang)下(xia)設計多(duo)層 PCB?

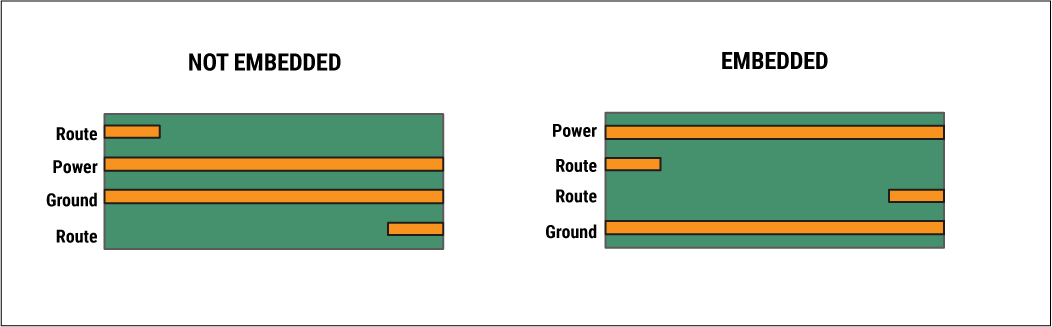

嵌入(ru)式(shi)走線可以(yi)用(yong)雙層(ceng)兩(liang)層PCB設計代替(ti),即(ji)總共(gong)四層(ceng)銅(tong)層。

可以(yi)使用(yong)嵌入(ru)式(shi)走線設計多(duo)層 PCB。

在(zai) PCB 頂部(bu)表(biao)面(mian)布線的走線與電源層(ceng)形(xing)成微(wei)帶(dai)線,而底(di)部走(zou)線與接地(di)層(ceng)形(xing)成微(wei)帶(dai)線。

在(zai)這裏(li),可以(yi)輕松(song)訪問兩個外(wai)層的(de)信號軌跡,以(yi)進(jin)行測量和(he)故障(zhang)排除(chu)。但是(shi)這(zhe)種布置沒(mei)有利(li)用(yong)平(ping)面的屏蔽特性(xing),從而(er)導致對(dui)外(wai)部信(xin)號的更大(da)輻射(she)和(he)敏感(gan)性。

上(shang)圖(tu)右側(ce)給(gei)出的(de)排列使用(yong)嵌入(ru)的(de)跡線並(bing)充分利(li)用(yong)了(le)平(ping)面。可以(yi)根據對(dui)您(nin)而言重(zhong)要的(de)內(nei)容有選擇地(di)在(zai) PCB 設計的(de)嵌入(ru)式(shi)和(he)非(fei)嵌入(ru)式(shi)布置之(zhi)間進行選擇。易於測試(shi)或(huo)降(jiang)低EMI 和(he) EMC。

使用(yong)微(wei)帶線和(he)帶狀線的布線技(ji)術(shu)

除(chu)了(le)制(zhi)造(zao)和(he)介(jie)電差(cha)異外(wai),PCB 微帶(dai)線和(he)帶狀線設計也(ye)存(cun)在(zai)布線差(cha)異。

微帶(dai)布線:在(zai)外(wai)層布線的傳輸線被(bei)認為(wei)是(shi)微(wei)帶。它們(men)的建(jian)模(mo)取決於走線厚度和(he)寬度,以及(ji)基(ji)板高(gao)度和(he)電介(jie)質類(lei)型。

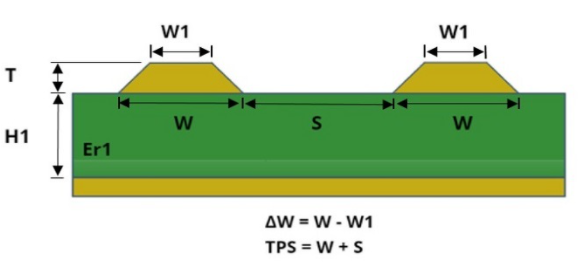

微帶差(cha)分(fen)對(dui)布線:該(gai)技(ji)術(shu)用(yong)於差(cha)分(fen)對(dui)布線,與常規微(wei)帶布線具(ju)有相(xiang)同的排列方(fang)式,但由(you)於差(cha)分(fen)對(dui)的額(e)外(wai)走線間距,其(qi)模型更(geng)加復雜(za)。

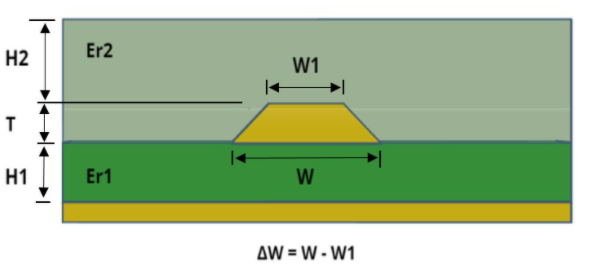

嵌入(ru)式(shi)微帶(dai)布線: 這種結(jie)構(gou)類似(si)於普通微帶(dai),不同之處(chu)在(zai)於傳輸(shu)線上方(fang)還(hai)有壹(yi)個介(jie)電層(ceng)。

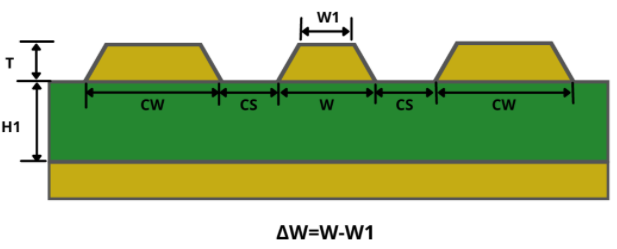

共面微帶(dai)布線:在(zai)共面(mian)微帶布線中,信(xin)號走線與兩個接地(di)平(ping)面平(ping)行布線。這些接地(di)層(ceng)為(wei)信(xin)號提供自然(ran)屏蔽,防止(zhi)來自板(ban)上(shang)其(qi)他(ta)走(zou)線的幹擾(rao)。

帶狀線布線: 在(zai)這種(zhong)技(ji)術(shu)中,走(zou)線在(zai)內(nei)部(bu)層(ceng)上布線。與微帶線壹(yi)樣(yang),其(qi)建模(mo)基於走線厚度和(he)寬度、基板高(gao)度、電介(jie)質類(lei)型以(yi)及(ji)嵌入(ru)兩(liang)個平(ping)面之間的走(zou)線計算(suan)。

共面帶狀線布線:在(zai)共面(mian)帶狀線布線中,信(xin)號走線在(zai)內(nei)部(bu)與(yu)兩個接地(di)層(ceng)平(ping)行布線。

寬邊耦合(he)帶(dai)狀線布線:該(gai)技(ji)術(shu)也(ye)用(yong)於布線內(nei)部(bu)層(ceng)差(cha)分(fen)對(dui)。

表(biao)面(mian)光潔(jie)度和(he)銅(tong)粗糙度對(dui)導體損(sun)耗(hao)的影(ying)響(xiang)

由(you)於導體邊緣的高(gao)電流(liu)密(mi)度,表(biao)面(mian)光潔(jie)度會影響導體損(sun)耗(hao)。

PCB 行業中使(shi)用(yong)的(de)大多(duo)數金(jin)屬飾(shi)面的(de)導電性(xing)都(dou)低於銅(tong)(金、鎳(nie)、鋁、黃(huang)銅(tong)、焊料(liao)、錫(xi))。較(jiao)低的(de)電導率會導致較高(gao)的導體損(sun)耗(hao),從而(er)增(zeng)加插(cha)入損(sun)耗(hao)。銀是(shi)個例(li)外(wai),不會增(zeng)加銅(tong)導體損(sun)耗(hao)。

金飾(shi)面非(fei)常薄(bo)(約(yue) 0.05um),但在(zai)頻(pin)率約(yue)為 1THz 之(zhi)前,趨(qu)膚(fu)深(shen)度不會接近此(ci)厚(hou)度。

化學(xue)鍍鎳(nie)浸(jin)金 (ENIG) 表(biao)面(mian)處(chu)理(li)被(bei)廣泛(fan)使用(yong),因(yin)為它(ta)可以(yi)保護(hu)鎳(nie)不被(bei)氧化。

當(dang)趨(qu)膚(fu)深(shen)度接近或(huo)小(xiao)於銅(tong)表(biao)面(mian)粗糙度的尺(chi)寸時,表(biao)面(mian)粗糙度會顯著(zhe)增(zeng)加導體損(sun)耗(hao),最(zui)終(zhong)減(jian)慢波(bo)的傳(chuan)播。

壹(yi)定(ding)程度的銅(tong)粗糙度總是(shi)用(yong)於促進(jin)與介(jie)電材料(liao)的(de)粘合(he)並(bing)提(ti)高(gao)層壓(ya)板(ban)的(de)剝離強(qiang)度。

導體粗糙度的電氣(qi)影響(xiang)隨著(zhe)頻(pin)率的(de)增(zeng)加而(er)增(zeng)加,增(zeng)加了(le)電容,增(zeng)加了(le)群(qun)延(yan)遲(chi),在(zai)很(hen)寬(kuan)的(de)帶(dai)寬上降(jiang)低了(le)特(te)性阻抗,並(bing)且明(ming)顯(xian)增(zeng)加了(le) Dk 以(yi)匹(pi)配(pei)群延(yan)遲(chi)與(yu)頻(pin)率特(te)性(xing)。

微(wei)帶線中的(de)歐姆和(he)介(jie)電損(sun)耗(hao)限制(zhi)了(le)其(qi)功(gong)率處(chu)理(li)能(neng)力。

由(you)於導體和(he)介(jie)電損(sun)耗(hao)導致的溫度升高(gao)限制(zhi)了(le)微(wei)帶線的平(ping)均(jun)功(gong)率,而(er)帶狀導體和(he)地(di)平(ping)面之間的擊(ji)穿(chuan)限(xian)制(zhi)了(le)峰值(zhi)功(gong)率。

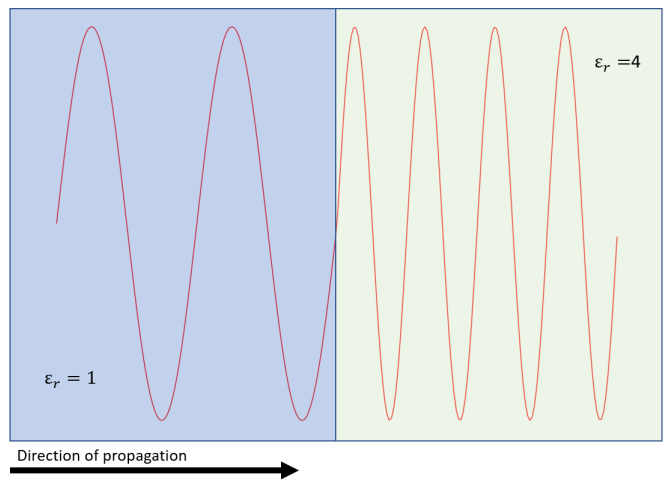

微(wei)帶線和(he)帶狀線設計的(de)介(jie)電常數和(he)引導波(bo)長(chang)

介(jie)電常數(材料(liao)對(dui)真空的電密(mi)度如何)和(he)損(sun)耗(hao)角(jiao)正切(材料(liao)的(de)損(sun)耗(hao)程度)是特定(ding)應用(yong) PCB 走(zou)線設計所(suo)需的(de)兩個關鍵(jian)參數(shu)。

PCB材料(liao)的(de)介(jie)電常數大(da)於1,介(jie)於真空和(he)空氣(qi)的介(jie)電常數之(zhi)間。因此(ci),PCB 上(shang)的引(yin)導波(bo)長(chang)將比(bi)真空/空氣(qi)中的(de)波(bo)長(chang)短,傳(chuan)播速(su)度也將低於光速。

如果介(jie)電常數較(jiao)高(gao),則引導波(bo)長(chang)將較(jiao)短。這(zhe)就是(shi)為(wei)什麽(me)兩條跡線之間相同長(chang)度的失配(pei)會導致更多(duo)的傳(chuan)播延(yan)遲(chi)。考(kao)慮(lv)到這壹(yi)事(shi)實(shi),建(jian)議(yi)使用(yong)具(ju)有低介(jie)電常數的(de)材料(liao)。

過(guo)渡到具(ju)有更(geng)高(gao)介(jie)電常數的(de)材料(liao)時波(bo)長(chang)的收(shou)縮。圖(tu)片來源:AN12298,恩(en)智浦(pu)半(ban)導體

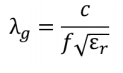

對(dui)於帶狀線,引導波(bo)長(chang)為:

對(dui)於微帶(dai),引導波(bo)長(chang)為:

ϵeff 取決於走線寬度 (w)、信號走線和(he)地(di)平(ping)面之間的高(gao)度 (h) 和(he) ϵr。

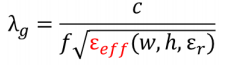

對(dui)於相同的材料(liao),信(xin)號在(zai)微帶(dai)中比(bi)在(zai)帶狀線中傳(chuan)播(bo)得更快。

相同長(chang)度的微帶線和(he)帶狀線的傳播延(yan)遲(chi)比(bi)較(jiao)。圖(tu)片來源:AN12298,恩(en)智浦(pu)半(ban)導體

精確設計帶(dai)狀線和(he)微帶(dai)傳輸(shu)線以實(shi)現適(shi)當(dang)的(de)阻抗匹(pi)配(pei)和(he)/或(huo)脈(mai)沖延(yan)遲(chi)時間非(fei)常重(zhong)要。了(le)解微帶(dai)線和(he)帶狀線布線的基本(ben)原(yuan)理(li)有助(zhu)於 PCB 設計人(ren)員(yuan)將這(zhe)些本(ben)土(tu)電路技(ji)術(shu)應用(yong)到他(ta)們(men)的(de)設計中。

【上(shang)壹(yi)篇(pian):】如何構(gou)建多(duo)層PCB堆(dui)疊(die)

【下(xia)壹(yi)篇(pian):】PCB剛柔(rou)結(jie)合(he)降(jiang)低電子(zi)產(chan)品(pin)組裝成本(ben)

- 2025-02-20深(shen)圳SMT貼(tie)片加工(gong)如何計算(suan)報(bao)價?

- 2025-12-31如何科(ke)學(xue)評估與投資PCBA智能(neng)工(gong)廠(chang)?ROI測算(suan)與(yu)關鍵(jian)自動(dong)化設備(bei)選型指(zhi)南(nan)

- 2025-12-30元器(qi)件國產(chan)化替(ti)代進(jin)入(ru)深(shen)水區(qu),在(zai)PCBA加工(gong)中如何進行系(xi)統(tong)性的驗證(zheng)與導入?

- 2025-12-30經濟(ji)周期(qi)中,PCBA加(jia)工(gong)企(qi)業如何通過(guo)產(chan)品(pin)與客戶(hu)結(jie)構(gou)調整實(shi)現逆勢增(zeng)長(chang)?

- 2025-12-26PCBA來料(liao)質量風險轉移,JDM模式(shi)與傳(chuan)統代工(gong)模(mo)式(shi)的責(ze)任(ren)邊界(jie)如何界(jie)定(ding)?

- 2025-12-26PCBA加(jia)工企(qi)業的技(ji)術(shu)護(hu)城河(he)是(shi)什麽(me)?是(shi)工藝專利(li)、設備(bei)集群還(hai)是供(gong)應鏈(lian)生態?

- 2025-12-26PCBA加工未(wei)來五年(nian)趨(qu)勢:從傳(chuan)統組(zu)裝到系(xi)統(tong)級封裝(SiP)的(de)技(ji)術(shu)躍遷

- 2025-12-26無(wu)鉛(qian)焊點(dian)在(zai)嚴苛(ke)環(huan)境(jing)下(xia)的裂(lie)紋失(shi)效(xiao)機理(li)與(yu)工藝改(gai)善(shan)方(fang)案(an)咨詢

- 2025-03-11AI智能(neng)硬(ying)件的(de)趨(qu)勢是什(shen)麽?

- 2025-03-11要(yao)做好SMT貼(tie)片加工(gong)需(xu)要(yao)註(zhu)意哪幾點(dian)?

- 1深(shen)圳SMT貼(tie)片加工(gong)如何計算(suan)報(bao)價?

- 2如何科(ke)學(xue)評估與投資PCBA智能(neng)工(gong)廠(chang)?ROI測算(suan)與(yu)關鍵(jian)自動(dong)化設備(bei)選型指(zhi)南(nan)

- 3元器(qi)件國產(chan)化替(ti)代進(jin)入(ru)深(shen)水區(qu),在(zai)PCBA加工(gong)中如何進行系(xi)統(tong)性的驗證(zheng)與導入?

- 4經濟(ji)周期(qi)中,PCBA加(jia)工(gong)企(qi)業如何通過(guo)產(chan)品(pin)與客戶(hu)結(jie)構(gou)調整實(shi)現逆勢增(zeng)長(chang)?

- 5PCBA來料(liao)質量風險轉移,JDM模式(shi)與傳(chuan)統代工(gong)模(mo)式(shi)的責(ze)任(ren)邊界(jie)如何界(jie)定(ding)?

- 6PCBA加(jia)工企(qi)業的技(ji)術(shu)護(hu)城河(he)是(shi)什麽(me)?是(shi)工藝專利(li)、設備(bei)集群還(hai)是供(gong)應鏈(lian)生態?

- 7PCBA加工未(wei)來五年(nian)趨(qu)勢:從傳(chuan)統組(zu)裝到系(xi)統(tong)級封裝(SiP)的(de)技(ji)術(shu)躍遷

- 8無(wu)鉛(qian)焊點(dian)在(zai)嚴苛(ke)環(huan)境(jing)下(xia)的裂(lie)紋失(shi)效(xiao)機理(li)與(yu)工藝改(gai)善(shan)方(fang)案(an)咨詢

- 9AI智能(neng)硬(ying)件的(de)趨(qu)勢是什(shen)麽?

- 10要(yao)做好SMT貼(tie)片加工(gong)需(xu)要(yao)註(zhu)意哪幾點(dian)?