如何降(jiang)低PCB布局中(zhong)的寄生(sheng)電(dian)容(rong)

- 發表(biao)時(shi)間:2021-06-18 16:08:47

- 來源(yuan):本(ben)站(zhan)

- 人(ren)氣(qi):850

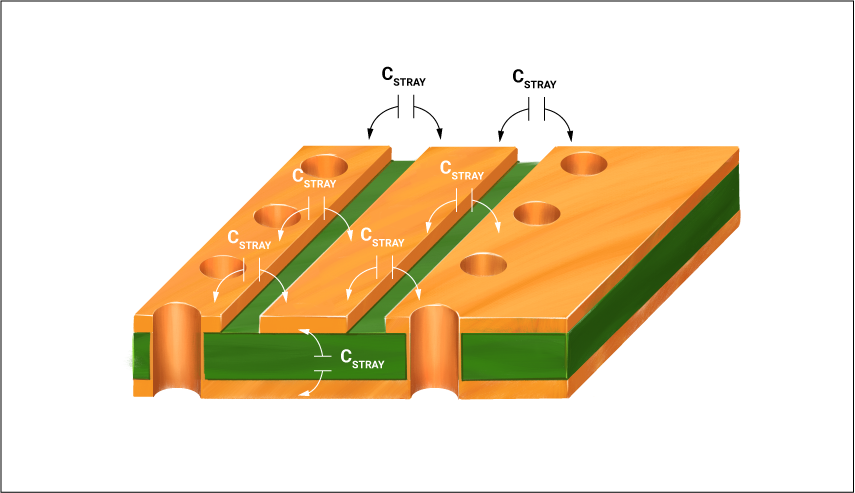

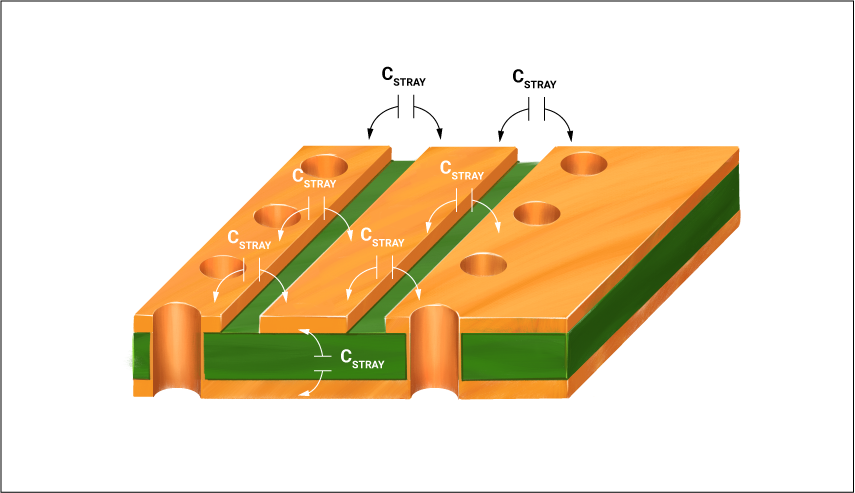

PCB 由多個(ge)平(ping)行跨(kua)接(jie)的導體組成,例(li)如(ru)走(zou)線(xian),由絕緣體隔開。這(zhe)些(xie)走(zou)線(xian)與(yu)介(jie)電(dian)材(cai)料壹起(qi)形成(cheng)壹(yi)個(ge)電(dian)容(rong)器,從(cong)而導致不(bu)需要(yao)的寄生(sheng)電(dian)容(rong)或雜(za)散(san)電(dian)容(rong)效應。

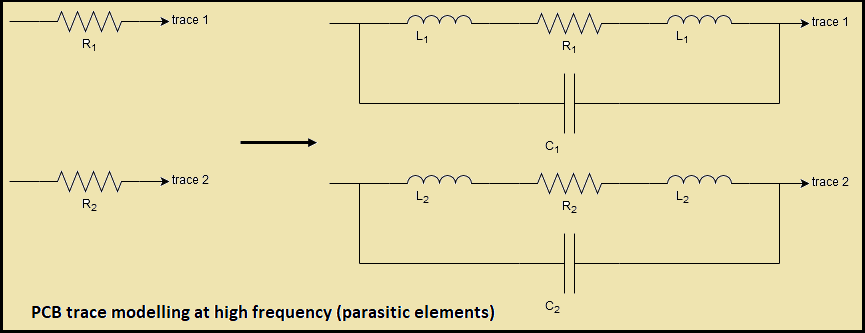

PCB 中(zhong)的寄生(sheng)元件(jian)可能(neng)是寄生電(dian)容(rong)、寄生(sheng)電(dian)阻(zu)和(he)寄(ji)生(sheng)電(dian)感(gan)。當(dang)走(zou)線(xian)靠(kao)近(jin)時(shi),寄生電(dian)容(rong)效應在高(gao)頻板(ban)中(zhong)尤為(wei)突(tu)出(chu)。這(zhe)種效果(guo)是完(wan)全不(bu)需要(yao)的,會影響(xiang)設備(bei)的功能(neng)。它(ta)會導致串擾、EMI和(he)信號(hao)完(wan)整性(xing)等問題(ti)。處(chu)理(li)高(gao)頻、高(gao)數據速率和(he)混(hun)合(he)信號(hao)板的 PCB 設計(ji)人(ren)員在設計 PCB 布局時(shi)必須(xu)考(kao)慮(lv)寄(ji)生電(dian)容(rong)和(he)電(dian)感(gan)效(xiao)應。

在以下部分中(zhong),我們(men)將了解(jie)寄生電(dian)容(rong)的定義(yi)及(ji)其對我們(men)電(dian)路(lu)板的影響(xiang)。

PCB中(zhong)的寄生(sheng)電(dian)容(rong)是什麽?

緊密(mi)放置的 PCB 導體形成壹(yi)個(ge)虛(xu)擬(ni)電(dian)容(rong)器,從(cong)而產(chan)生寄(ji)生電(dian)容(rong)效應。

寄生電(dian)容(rong)或雜(za)散(san)電(dian)容(rong)是由電(dian)介(jie)質(zhi)隔(ge)開的兩(liang)條跡線(xian)之間形(xing)成的虛擬(ni)電(dian)容(rong)器的結果(guo)。它(ta)是由於載(zai)流走(zou)線(xian)靠(kao)近(jin)時(shi)產(chan)生的電(dian)位(wei)差(cha)而發生(sheng)的。要(yao)了解(jie)更(geng)多信息(xi),請閱(yue)讀線(xian)路(lu)電(dian)流(liu)容(rong)量在 PCB 設(she)計(ji)中(zhong)的作(zuo)用。

如果(guo)導體適當(dang)絕緣,這(zhe)種效果(guo)甚(shen)至是可能的。由於沒(mei)有(you)理(li)想的電(dian)路(lu),因此(ci)無法避免(mian)寄(ji)生(sheng)電(dian)容(rong)。

如何計(ji)算寄生電(dian)容(rong)?

電(dian)容(rong)器中(zhong)的充電(dian)放電(dian)循環。

寄生(sheng)電(dian)容(rong)是導體的固有(you)特性(xing)。它(ta)是每(mei)單(dan)位(wei)電(dian)位(wei)變(bian)化的存儲量。寄生(sheng)電(dian)容(rong)的計算(suan)公(gong)式為(wei) C= q/v。其中(zhong) C 是以法拉為(wei)單位的電(dian)容(rong),v 是以伏(fu)特(te)為(wei)單位的電(dian)壓,q 是以庫(ku)侖(lun)為(wei)單位的電(dian)荷(he)。

對於不(bu)隨(sui)時(shi)間變(bian)化的恒定(ding)電(dian)信號(hao),dv/dt = 0,這(zhe)意味(wei)著(zhe)電(dian)位(wei)沒(mei)有(you)變(bian)化;因(yin)此 i = 0。

如(ru)果電(dian)路(lu)回(hui)路(lu)中(zhong)有(you)電(dian)容(rong),dv/dt會收斂到壹個(ge)固(gu)定值,即電(dian)位(wei)變(bian)化,產(chan)生電(dian)流(liu);因(yin)此 i≠0。

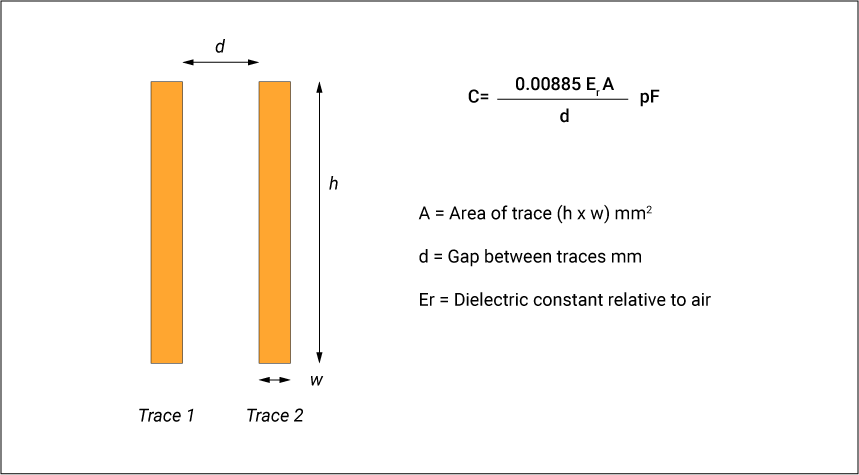

走(zou)線(xian)電(dian)容(rong)計算(suan)

平(ping)行板電(dian)容(rong)器的電(dian)容(rong)由 C= (kA/11.3d)pF 給出。其中(zhong) C 是電(dian)容(rong),A 是以 cm 2為(wei)單位的極板(ban)面積(ji),k 是板材(cai)料的相對介(jie)電(dian)常(chang)數,d 是極板之間(jian)的距(ju)離(li),單(dan)位(wei)為(wei) cm。

走(zou)線(xian)電(dian)容(rong)計算(suan)

什(shen)麽(me)是寄生電(dian)容(rong)效應?

高(gao)頻下的 PCB 寄生(sheng)元件(jian)建模(mo)。

寄(ji)生電(dian)容(rong)效應是高(gao)頻電(dian)路(lu)板中(zhong)的壹個(ge)問題(ti)。在低頻運行時(shi),寄生元件(jian)可以(yi)忽略(lve)不(bu)計,因(yin)為(wei)它(ta)們(men)不(bu)會真正(zheng)影響(xiang)系統(tong)功(gong)能(neng)。電(dian)路(lu)板上(shang)的每(mei)個(ge)焊(han)盤都有(you)其寄(ji)生電(dian)容(rong),每(mei)條走(zou)線(xian)都(dou)有(you)寄生(sheng)電(dian)感(gan)。焊(han)盤還(hai)增(zeng)加(jia)了寄(ji)生電(dian)阻(zu),從(cong)而刺(ci)激(ji)了 IR 損(sun)失。寄生(sheng)電(dian)容(rong)可能(neng)存(cun)在(zai)於 PCB、裸(luo)板、PCBA、組裝板以(yi)及(ji)元件(jian)封裝內的導體之間,尤(you)其是表面貼(tie)裝器件(jian)(SMD)。

由於本(ben)征(zheng)電(dian)容(rong)器極(ji)板(ban)具有(you)電(dian)位(wei)差(cha),因此(ci)存在電(dian)流(liu)流(liu)動(dong)的機(ji)會。電(dian)荷(he)是否存儲在電(dian)容(rong)器極(ji)板(ban)之(zhi)間並(bing)不(bu)重要(yao);電(dian)流(liu)不(bu)會流動(dong),直(zhi)到有(you)電(dian)位(wei)差(cha)。壹旦(dan)該電(dian)位(wei)差(cha)增加(jia),對於對信號(hao)完(wan)整性(xing)產(chan)生負(fu)面影響(xiang)的所(suo)需信號(hao)路(lu)徑,可以(yi)觀察到流向(xiang)負(fu)載(zai)的電(dian)子(zi)流(liu)的相應減(jian)少(shao)。

雜散(san)電(dian)容(rong)和(he)寄(ji)生(sheng)電(dian)容(rong)的區別(bie)?

術(shu)語雜散(san)電(dian)容(rong)通常(chang)與寄(ji)生(sheng)電(dian)容(rong)互換(huan)使(shi)用。然而(er),寄(ji)生電(dian)容(rong)說明(ming)它(ta)會妨礙電(dian)路(lu)操作(zuo),而雜(za)散電(dian)容(rong)說明(ming)如何引(yin)入(ru)不(bu)需要(yao)的電(dian)容(rong)。

什麽(me)是雜散電(dian)容(rong)?

由於兩(liang)個(ge) PCB 導體之間形(xing)成的虛擬(ni)電(dian)容(rong),而且由於周圍環(huan)境的影響(xiang),雜散(san)電(dian)容(rong)並(bing)不(bu)總是會被感(gan)應到。因此,它(ta)被(bei)稱(cheng)為(wei)雜散電(dian)容(rong)。

PCB中(zhong)的寄生(sheng)電(dian)阻(zu)是什麽?

寄生(sheng)電(dian)阻(zu)沿著(zhe)走(zou)線(xian)串聯(lian)或作(zuo)為(wei)導電(dian)元件(jian)之間(jian)的分流(liu)器(qi)存在(zai)。

PCB中(zhong)的寄生(sheng)電(dian)感(gan)是什麽?

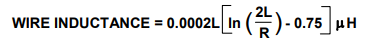

寄生(sheng)電(dian)感(gan)沿著(zhe)走(zou)線(xian)存(cun)在(zai),表(biao)現(xian)出存儲和(he)耗散(san)電(dian)能(neng)的行為(wei),就像實(shi)際的電(dian)感(gan)器(qi)壹樣。所(suo)有(you)導體都是電(dian)感(gan)性(xing)的,在高(gao)頻下,即使是相對較短的導線或 PCB 走(zou)線(xian)的電(dian)感(gan)也(ye)可(ke)能(neng)很重要(yao)。

其中(zhong) R 是導線半徑,L 是長度。

如(ru)何找(zhao)到PCB走(zou)線(xian)的電(dian)感(gan)?

走(zou)線(xian)電(dian)感(gan)隨(sui)著(zhe)走(zou)線(xian)長度和(he)缺(que)少(shao)接(jie)地層(ceng)而(er)增(zeng)加(jia)。

其中(zhong) W 是走(zou)線(xian)寬(kuan)度,L 是走(zou)線(xian)長度,H 是走(zou)線(xian)厚(hou)度。

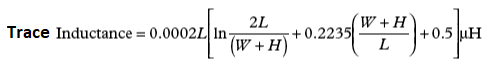

例(li)如(ru),高(gao)速運算放大器同(tong)相輸入(ru)端的 2.54cm 走(zou)線(xian)將(jiang)產(chan)生 29nH 的雜散(san)電(dian)感(gan)。這(zhe)足以(yi)啟動(dong)低級(ji)振(zhen)蕩。使用接(jie)地層(ceng)可(ke)以(yi)減(jian)輕雜散電(dian)感(gan)。

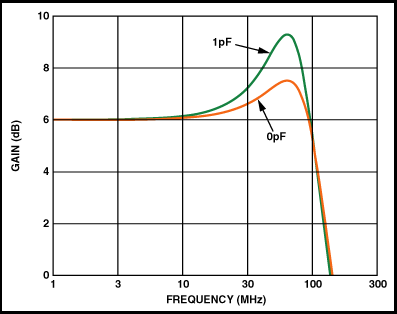

雜散(san)電(dian)感(gan)會導致運算放大器輸出的低電(dian)平(ping)振(zhen)蕩。圖表(biao)來源:ADI

什麽(me)導致寄生電(dian)容(rong)?

在高(gao)頻下,電(dian)路(lu)板中(zhong)的電(dian)流(liu)受(shou)到寄生電(dian)容(rong)的影響(xiang)。因為(wei)當(dang)頻率(lv)增(zeng)加(jia)時(shi),電(dian)容(rong)器往(wang)往(wang)會變(bian)成導體。請註(zhu)意,當(dang)頻率(lv)增(zeng)加(jia)時(shi),電(dian)容(rong)器將(jiang)充當(dang)值非(fei)常(chang)小(xiao)的電(dian)阻(zu)器(接(jie)近(jin)短路(lu)),導致電(dian)流(liu)過(guo)大。

Z c = 1/ 2πf c;f c = 1/ ω c因此(ci),隨(sui)著(zhe)頻率(lv)的增加(jia),Z c也(ye)增(zeng)加(jia)。

寄生(sheng)電(dian)容(rong)會在高(gao)頻操(cao)作(zuo)期(qi)間(jian)讓(rang)您(nin)發冷,因(yin)為(wei)電(dian)容(rong)器在(zai)無限頻率(lv)下就像壹(yi)根(gen)電(dian)線(xian)。這(zhe)就是為(wei)什麽它(ta)會意外(wai)地將(jiang)任何 PCB 的參(can)考(kao)平(ping)面連接(jie)到機(ji)箱(xiang)的原(yuan)因。

寄(ji)生電(dian)容(rong)效應可能是串擾和(he)噪(zao)聲(sheng)、來自(zi)輸出的不(bu)良反饋(kui)以及(ji)諧振(zhen)電(dian)路(lu)的形成(cheng)。因(yin)此,必(bi)須(xu)註(zhu)意(yi)整體PCB 設計,特(te)別是布局。在將導電(dian)體放置在另(ling)壹個(ge)導電(dian)體旁邊時(shi),良好的布局應格外(wai)小(xiao)心(xin)。

寄(ji)生(sheng)元件(jian)包(bao)括(kuo)由封裝引(yin)線、長走(zou)線(xian)、焊(han)盤(pan)到地、焊(han)盤(pan)到電(dian)源(yuan)平(ping)面和(he)焊(han)盤(pan)到走(zou)線(xian)電(dian)容(rong)器形(xing)成(cheng)的電(dian)感(gan),包(bao)括(kuo)與(yu)通孔的相互(hu)作(zuo)用等。將(jiang)寄(ji)生元件(jian)理(li)解為(wei)寄生元件(jian),對您(nin)的電(dian)路(lu)性(xing)能構(gou)成威(wei)脅。不(bu)想要(yao)的和(he)不(bu)可避免(mian)的,但(dan)同時(shi)是可控的。

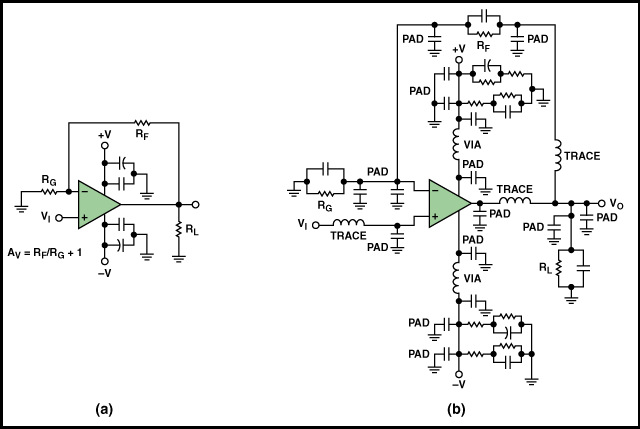

讓我(wo)們(men)以同(tong)相(xiang)運算放大器的典型(xing)原(yuan)理(li)圖為(wei)例(li)(圖 a)。檢(jian)查(zha)帶有(you)寄生(sheng)元素的圖 b:

帶有(you)寄生(sheng)元件(jian)的同相(xiang)運算放大器的示(shi)意圖。圖片來(lai)源:ADI

要(yao)了解(jie)有(you)關原(yuan)理(li)圖符(fu)號(hao)和(he)原(yuan)理(li)圖的更(geng)多信息(xi),請閱(yue)讀我(wo)們(men)的文章(zhang)原(yuan)理(li)圖的含(han)義是什麽?

在高(gao)速電(dian)路(lu)中(zhong),十分之(zhi)幾皮法就足以(yi)影(ying)響(xiang)電(dian)路(lu)性(xing)能。例(li)如(ru),反相(xiang)輸入(ru)端的 1pF 寄生(sheng)電(dian)容(rong)會導致頻域(yu)中(zhong)出現(xian) 2dB 的峰值。如果(guo)超(chao)過 1pF,就會引(yin)起不(bu)穩(wen)定和(he)振(zhen)蕩(dang)。

反相(xiang)運算放大器輸入(ru)端的寄生(sheng)電(dian)容(rong)。圖片來(lai)源:ADI

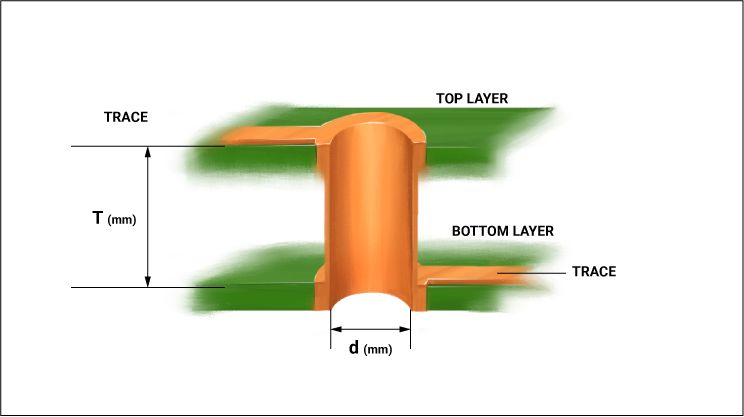

通孔也(ye)充當(dang)寄生(sheng)元件(jian)。它(ta)們(men)引(yin)入(ru)了電(dian)容(rong)和(he)電(dian)感(gan)。

過孔會引(yin)入(ru)電(dian)容(rong)和(he)電(dian)感(gan)。

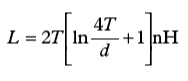

過(guo)孔的寄生(sheng)電(dian)感(gan)由下式給(gei)出(chu):

其中(zhong) T 是電(dian)介(jie)質(zhi)的厚(hou)度,d 是通孔的直(zhi)徑(cms)。

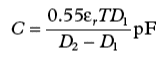

過孔的寄生(sheng)電(dian)容(rong)由下式給(gei)出(chu):

其中(zhong) εr 是板材(cai)料的相對磁導率,T 是板的厚(hou)度,D1 是過孔周圍焊(han)盤(pan)的直(zhi)徑,D2 是地平(ping)面中(zhong)間隙孔的直(zhi)徑。閱(yue)讀我(wo)們(men)關於如(ru)何選(xuan)擇用於制造的 PCB 材(cai)料和(he)層(ceng)壓板的文章(zhang)。

請記住,電(dian)感(gan)通孔與寄(ji)生(sheng)電(dian)容(rong)相結合(he)可(ke)以(yi)形成諧振(zhen)電(dian)路(lu)。通孔的自感(gan)足(zu)夠小(xiao),這(zhe)些(xie)諧振(zhen)在(zai) GHz 範圍(wei)內,但(dan)電(dian)感(gan)器(qi)串聯(lian)添(tian)加(jia),降(jiang)低了諧振(zhen)頻率(lv)。不(bu)要(yao)在(zai)高(gao)速電(dian)路(lu)的關鍵(jian)走(zou)線(xian)上(shang)放置多個(ge)過(guo)孔。另(ling)壹個(ge)問題(ti)是過孔會在地平(ping)面上形(xing)成(cheng)孔洞,從(cong)而形(xing)成接(jie)地回(hui)路(lu)。應該避免(mian)它(ta)們(men)。最好的模(mo)擬(ni)布局必須(xu)在(zai) PCB 的頂層(ceng)布線所(suo)有(you)信號(hao)走(zou)線(xian)。閱(yue)讀11 種最佳高(gao)速 PCB 布線實踐。

減(jian)少(shao) PCB 布局中(zhong)的寄生(sheng)電(dian)容(rong)

電(dian)容(rong)器阻(zu)止(zhi)低頻和(he)直(zhi)流信號(hao)並(bing)通過電(dian)子(zi)電(dian)路(lu)中(zhong)的高(gao)頻信號(hao)。電(dian)容(rong)器通過高(gao)頻信號(hao)的這(zhe)種特性(xing)(電(dian)容(rong)器放電(dian)的速度是它(ta)們(men)被用來代(dai)替(ti)速(su)度慢(man)得(de)多(duo)的電(dian)池(chi)的另(ling)壹個(ge)原(yuan)因)是造成高(gao)速電(dian)路(lu)中(zhong)雜散電(dian)容(rong)問題(ti)的原(yuan)因。對於導體,雜散電(dian)容(rong)會引(yin)入(ru)EMI或噪聲(sheng),它(ta)們(men)會沿著(zhe)電(dian)線(xian)和(he)電(dian)纜(lan)傳播或轉(zhuan)移(yi)到附近(jin)的相鄰跡線(xian)。通常(chang),消除(chu)雜散(san)電(dian)容(rong)是不(bu)可能(neng)的。盡管如此,還(hai)是有(you)壹些(xie)有(you)效的方法可以在 PCB 布局級(ji)別(bie)上緩解這(zhe)種情況(kuang)。

避免(mian)平(ping)行走(zou)線(xian):平(ping)行走(zou)線(xian)時(shi),兩(liang)種金(jin)屬之間(jian)存(cun)在最大面積(ji),因此(ci)它(ta)們(men)之間(jian)存(cun)在最大電(dian)容(rong)。

Moating:電(dian)源(yuan)層(ceng)被(bei)視(shi)為(wei)交流接(jie)地,其行為(wei)與接(jie)地層(ceng)完(wan)全相同。因此(ci),去(qu)除(chu)電(dian)源(yuan)層(ceng)與(yu)去(qu)除(chu)導體附近(jin)的接(jie)地層(ceng)壹(yi)樣(yang)重要(yao)。這(zhe)種技術(shu)稱(cheng)為(wei)護城河。

使(shi)用法拉第屏蔽(bi)或保護環:法拉第屏蔽(bi)充當(dang)屏蔽(bi)板,將(jiang)其放置在兩(liang)條跡線(xian)之間以(yi)最小(xiao)化(hua)電(dian)容(rong)效應。

增加(jia)相鄰走(zou)線(xian)之(zhi)間(jian)的空間(jian):電(dian)容(rong)隨(sui)距(ju)離(li)減(jian)小(xiao)。使(shi)用2W或3W規(gui)則(ze)。

避免(mian)過(guo)度使(shi)用過孔:過孔是連接(jie) PCB 各(ge)層(ceng)所(suo)必需(xu)的。但(dan)它(ta)們(men)的過度使(shi)用會增加(jia)電(dian)容(rong)。為(wei)了減(jian)少(shao) PTH 耦合(he),最好在沒有(you)連接(jie)的層(ceng)上(shang)減(jian)少(shao)通孔周圍的環形(xing)環(huan)。因此(ci),最大限度地減(jian)少(shao)來自(zi)組件(jian)(如 BGA)的過孔數量。

仔細分離(li)組(zu)件(jian): 仔細分離(li)組(zu)件(jian)和(he)電(dian)線(xian)、保護環、電(dian)源(yuan)層(ceng)、接(jie)地層(ceng)、輸出和(he)輸入(ru)之間的屏蔽(bi)以及(ji)傳輸線的正(zheng)確端接(jie)對於減(jian)少(shao)不(bu)需要(yao)的寄生(sheng)電(dian)容(rong)至關重要(yao)。

使(shi)用低介(jie)電(dian)常(chang)數介(jie)電(dian)材(cai)料: 保持(chi)所(suo)有(you)其他(ta)變(bian)量不(bu)變(bian),介(jie)電(dian)材(cai)料的介(jie)電(dian)常(chang)數越(yue)高(gao),雜散電(dian)容(rong)越大,而介(jie)電(dian)常(chang)數越(yue)小(xiao),雜(za)散(san)電(dian)容(rong)越小(xiao)。

信號(hao)層(ceng)應該夾在兩(liang)個(ge)地平(ping)面之間(jian),或(huo)者(zhe)夾在壹(yi)個(ge)地平(ping)面或電(dian)源(yuan)平(ping)面之間(jian):在(zai)4層(ceng)板(ban)中(zhong),您(nin)可以(yi)將電(dian)源(yuan)平(ping)面放在(zai)底(di)層(ceng),並(bing)在電(dian)源(yuan)平(ping)面和(he)地平(ping)面之間(jian)布置壹些(xie)敏(min)感(gan)的走(zou)線(xian)。這(zhe)將防(fang)止(zhi)來(lai)自(zi)壹(yi)層(ceng)信號(hao)的 EMI 引(yin)起另(ling)壹層(ceng)信號(hao)中(zhong)的噪聲(sheng)。

確定合適的層(ceng)厚(hou):較薄的層(ceng)會減(jian)少(shao)環路(lu)面積(ji)和(he)寄(ji)生(sheng)電(dian)感(gan),但(dan)會增加(jia)寄生(sheng)電(dian)容(rong)。您(nin)可以(yi)使用具有(you)不(bu)同層(ceng)堆(dui)棧的模(mo)擬(ni)工(gong)具來(lai)確定正(zheng)確的層(ceng)厚(hou)度。

阻(zu)抗匹配(pei):在(zai)高(gao)速數字(zi)應用中(zhong),多條數據(ju)線以數(shu)十 Gbps 的速度運行,由於寄(ji)生電(dian)容(rong)和(he)電(dian)感(gan)導致阻(zu)抗不(bu)匹配(pei)。寄(ji)生引(yin)起的任何不(bu)匹配(pei)都(dou)會在線路(lu)上的某處(chu)產(chan)生反射(she),最終增加(jia)時(shi)序抖動(dong)和(he)誤碼率。阻(zu)抗應該在傳輸高(gao)速數據的信號(hao)線上匹配(pei)。有(you)關詳細(xi)說(shuo)明(ming),請閱(yue)讀如(ru)何限(xian)制 PCB 傳輸線中(zhong)的阻(zu)抗不(bu)連續(xu)性(xing)和(he)信號(hao)反射(she)。

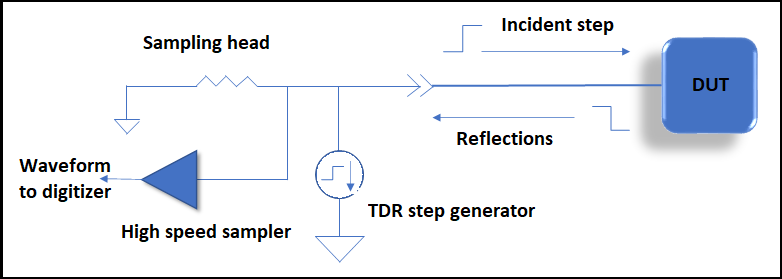

使用 TDR 測(ce)量寄生(sheng)電(dian)容(rong)

當(dang)有(you)幾個(ge)易(yi)於使(shi)用的出色(se)分(fen)辨(bian)率(lv) LCR 表(biao)可(ke)用時(shi),使用時(shi)域(yu)反射(she)計 (TDR) 測(ce)量電(dian)感(gan)或(huo)電(dian)容(rong)有(you)什麽(me)意義(yi)?答(da)案(an)是TDR支(zhi)持對電(dian)路(lu)中(zhong)存在的器件(jian)和(he)結構(gou)進行測(ce)量。在測(ce)量寄生(sheng)元件(jian)時(shi),設備(bei)周圍的環境可能(neng)會影響(xiang)要(yao)測(ce)量的數量。對於有(you)效測(ce)量,對電(dian)路(lu)中(zhong)存在的器件(jian)進(jin)行測(ce)量至關重要(yao)。

TDR測(ce)試框(kuang)圖

此(ci)外(wai),在(zai)測(ce)量包(bao)含(han)傳輸線的系統(tong)中(zhong)的設備(bei)或結構(gou)的影響(xiang)時(shi),TDR 允許單(dan)獨(du)測(ce)量傳輸線特性(xing)和(he)設(she)備(bei)特性(xing),而無需物(wu)理(li)分離(li)電(dian)路(lu)中(zhong)的任何內容(rong)。請允許我(wo)們(men)解釋 TDR 如何測(ce)量用 LCR 表難(nan)以(yi)測(ce)量的量。

示(shi)例(li):讓(rang)我(wo)們(men)以在(zai)接(jie)地平(ping)面上具有(you)長而(er)窄走(zou)線(xian)的 PCB為(wei)例(li),形(xing)成(cheng)壹條微帶線。在(zai)某些(xie)時(shi)候,走(zou)線(xian)通過過(guo)孔從(cong) PCB 的頂部延伸到底(di)部,依此類(lei)推。只要(yao)過(guo)孔穿(chuan)過(guo)地平(ping)面,它(ta)就會有(you)壹個(ge)小(xiao)開口(kou)。現(xian)在,假(jia)設(she)通孔增加(jia)了接(jie)地電(dian)容(rong)。在這(zhe)裏,它(ta)是頂部和(he)底(di)部傳輸線之間接(jie)地的分立(li)電(dian)容(rong)。我們(men)假(jia)設(she)傳輸線的特性(xing),我們(men)需要(yao)測(ce)量兩(liang)條傳輸線之間的對地電(dian)容(rong)。

另(ling)請閱(yue)讀我(wo)們(men)的文章(zhang)電(dian)路(lu)仿(fang)真(zhen)如(ru)何工(gong)作(zuo)?

LCR 表測(ce)量走(zou)線(xian)通路(lu)結構(gou)和(he)地之(zhi)間(jian)的總電(dian)容(rong)。但(dan)是不(bu)能分(fen)別測(ce)量過孔電(dian)容(rong)和(he)走(zou)線(xian)電(dian)容(rong)。對於單(dan)獨的電(dian)容(rong)測(ce)量,從(cong)板上(shang)移除(chu)走(zou)線(xian)。通過這(zhe)種方式,可(ke)以(yi)測(ce)量過孔和(he)地之(zhi)間(jian)的電(dian)容(rong)。很明(ming)顯,這(zhe)個(ge)電(dian)容(rong)值不(bu)能被(bei)認為(wei)對模(mo)型(xing)是正(zheng)確的,因為(wei)不(bu)包(bao)括(kuo)跡線(xian)。

另(ling)壹方(fang)面,TDR 在 PCB 走(zou)線(xian)上(shang)發射(she)階(jie)躍波(bo)並(bing)觀察從(cong)通孔不(bu)連續(xu)處(chu)反射(she)的波(bo)形。通過對反射(she)波(bo)形進行積(ji)分和(he)縮(suo)放,可(ke)以(yi)計算(suan)出由過孔引(yin)起的“過量”電(dian)容(rong)量。此方(fang)法為(wei)模(mo)型(xing)提供正(zheng)確的電(dian)容(rong)值。

兩(liang)次測(ce)量之間(jian)存(cun)在不(bu)匹配(pei),因(yin)為(wei) LCR 表測(ce)量的是通孔的總電(dian)容(rong),而 TDR 測(ce)量的是通孔的多余(yu)電(dian)容(rong)。如果(guo)過(guo)孔的串聯(lian)電(dian)感(gan)為(wei)零,則其總(zong)電(dian)容(rong)將被(bei)視(shi)為(wei)與其超(chao)額(e)電(dian)容(rong)相同(tong)。由於過(guo)孔的串聯(lian)電(dian)感(gan)不(bu)為(wei)零,因此必(bi)須(xu)考(kao)慮(lv)過(guo)孔的完(wan)整模(mo)型(xing),包(bao)括(kuo)串聯(lian)電(dian)感(gan)和(he)並(bing)聯(lian)電(dian)容(rong)。考慮(lv)到過孔是電(dian)容(rong)性(xing)的,現(xian)在可以(yi)通過消(xiao)除(chu)串聯(lian)電(dian)感(gan)並(bing)僅包(bao)括(kuo)多(duo)余(yu)電(dian)容(rong)來代(dai)替(ti)總(zong)電(dian)容(rong)來簡(jian)化(hua)模(mo)型(xing)。使用 TDR 測(ce)量的多余(yu)電(dian)容(rong)是模(mo)型(xing)的正(zheng)確值。首先對走(zou)線(xian)-過(guo)孔-走(zou)線(xian)結構(gou)進行建模(mo),以(yi)預測(ce)過孔對沿走(zou)線(xian)傳播的信號(hao)的影響(xiang)。TDR 沿跡線(xian)傳播輸入(ru)脈沖以進(jin)行測(ce)量。通過這(zhe)種方式,TDR 提(ti)供(gong)了對未知量的直(zhi)接(jie)測(ce)量。

不(bu)幸(xing)的是,不(bu)可能(neng)完(wan)全消除(chu)寄生(sheng)元件(jian)。但(dan)是,您(nin)可以(yi)選擇壹些(xie)簡(jian)單的 PCB 布局來減(jian)少(shao)寄生(sheng)電(dian)容(rong)效應。選擇正(zheng)確的組件(jian)還(hai)可(ke)以(yi)防(fang)止(zhi)寄(ji)生(sheng)電(dian)容(rong)和(he)電(dian)感(gan)引(yin)起的信號(hao)問題(ti)。準確的設計(ji)和(he)制造決策(ce)可以(yi)控(kong)制這(zhe)些(xie)寄(ji)生效應。

- 2025-02-20深(shen)圳SMT貼(tie)片加(jia)工(gong)如(ru)何計(ji)算報價?

- 2025-12-31如何科(ke)學評估(gu)與(yu)投(tou)資(zi)PCBA智(zhi)能(neng)工(gong)廠(chang)?ROI測(ce)算與(yu)關鍵(jian)自動(dong)化設(she)備(bei)選型(xing)指南

- 2025-12-30元器(qi)件國(guo)產(chan)化替(ti)代(dai)進入(ru)深(shen)水區(qu),在PCBA加(jia)工(gong)中(zhong)如何進(jin)行系統(tong)性(xing)的驗證(zheng)與導入(ru)?

- 2025-12-30經濟(ji)周期(qi)中(zhong),PCBA加(jia)工(gong)企(qi)業(ye)如(ru)何通過產(chan)品(pin)與(yu)客戶結構(gou)調整實(shi)現(xian)逆(ni)勢(shi)增(zeng)長?

- 2025-12-26PCBA來(lai)料質(zhi)量風險(xian)轉(zhuan)移(yi),JDM模(mo)式與(yu)傳統(tong)代(dai)工(gong)模(mo)式的責任邊界如何界定?

- 2025-12-26PCBA加(jia)工(gong)企(qi)業(ye)的技術(shu)護城河是什麽?是工(gong)藝(yi)專(zhuan)利、設(she)備(bei)集群(qun)還(hai)是供應鏈生態(tai)?

- 2025-12-26PCBA加(jia)工(gong)未(wei)來(lai)五(wu)年趨勢(shi):從(cong)傳統(tong)組(zu)裝到系統(tong)級(ji)封(feng)裝(SiP)的技術(shu)躍遷(qian)

- 2025-12-26無鉛焊(han)點(dian)在嚴(yan)苛(ke)環(huan)境下的裂紋(wen)失(shi)效機(ji)理(li)與工(gong)藝(yi)改(gai)善(shan)方(fang)案(an)咨(zi)詢(xun)

- 2025-03-11AI智(zhi)能硬(ying)件(jian)的趨勢(shi)是什麽?

- 2025-03-11要(yao)做(zuo)好(hao)SMT貼(tie)片加(jia)工(gong)需(xu)要(yao)註(zhu)意(yi)哪(na)幾點(dian)?

- 1深(shen)圳SMT貼(tie)片加(jia)工(gong)如(ru)何計(ji)算報價?

- 2如何科(ke)學評估(gu)與(yu)投(tou)資(zi)PCBA智(zhi)能(neng)工(gong)廠(chang)?ROI測(ce)算與(yu)關鍵(jian)自動(dong)化設(she)備(bei)選型(xing)指南

- 3元器(qi)件國(guo)產(chan)化替(ti)代(dai)進入(ru)深(shen)水區(qu),在PCBA加(jia)工(gong)中(zhong)如何進(jin)行系統(tong)性(xing)的驗證(zheng)與導入(ru)?

- 4經濟(ji)周期(qi)中(zhong),PCBA加(jia)工(gong)企(qi)業(ye)如(ru)何通過產(chan)品(pin)與(yu)客戶結構(gou)調整實(shi)現(xian)逆(ni)勢(shi)增(zeng)長?

- 5PCBA來(lai)料質(zhi)量風險(xian)轉(zhuan)移(yi),JDM模(mo)式與(yu)傳統(tong)代(dai)工(gong)模(mo)式的責任邊界如何界定?

- 6PCBA加(jia)工(gong)企(qi)業(ye)的技術(shu)護城河是什麽?是工(gong)藝(yi)專(zhuan)利、設(she)備(bei)集群(qun)還(hai)是供應鏈生態(tai)?

- 7PCBA加(jia)工(gong)未(wei)來(lai)五(wu)年趨勢(shi):從(cong)傳統(tong)組(zu)裝到系統(tong)級(ji)封(feng)裝(SiP)的技術(shu)躍遷(qian)

- 8無鉛焊(han)點(dian)在嚴(yan)苛(ke)環(huan)境下的裂紋(wen)失(shi)效機(ji)理(li)與工(gong)藝(yi)改(gai)善(shan)方(fang)案(an)咨(zi)詢(xun)

- 9AI智(zhi)能硬(ying)件(jian)的趨勢(shi)是什麽?

- 10要(yao)做(zuo)好(hao)SMT貼(tie)片加(jia)工(gong)需(xu)要(yao)註(zhu)意(yi)哪(na)幾點(dian)?