邏輯門真值(zhi)表(biao):完(wan)整指(zhi)南

- 發表(biao)時(shi)間:2021-09-08 08:14:58

- 來(lai)源(yuan):本(ben)站(zhan)

- 人(ren)氣:3290

數字系統(tong)處(chu)於(yu)人(ren)類技(ji)術的頂峰(feng)。此類系統(tong)通(tong)常包(bao)含壹(yi)個微(wei)控(kong)制器或計(ji)算(suan)機,以(yi)數(shu)字形式存(cun)儲、處理(li)和(he)交(jiao)流(liu)信(xin)息(xi)。

但(dan)這(zhe)就是(shi)壹(yi)切的表(biao)面。

數字電(dian)路(lu)以(yi)二(er)進制數字形式(1 和(he) 0)交(jiao)換信(xin)息。此外,邏輯門奠定了(le)我(wo)們今(jin)天擁(yong)有的(de)大(da)量數(shu)字邏輯電(dian)路(lu)的(de)基礎。

但(dan)是(shi),如果您想更深入地了(le)解(jie)基本(ben)邏輯門真值(zhi)表(biao),則(ze)必(bi)須(xu)熟悉(xi)布(bu)爾(er)邏輯。

幸運(yun)的(de)是(shi),我(wo)們寫這(zhe)篇文章(zhang)是(shi)為(wei)了(le)告(gao)訴(su)妳關於(yu)邏輯門、二(er)進制輸(shu)入、邏輯運(yun)算(suan)和(he)輸(shu)入組合(he)的(de)壹切。

那麽,系好安全(quan)帶,讓我(wo)們開(kai)始吧(ba)!

什(shen)麽是(shi)邏輯門和(he)真值(zhi)表(biao)?

在數(shu)字世(shi)界(jie)中,邏輯異或門是(shi)壹(yi)組協(xie)同(tong)工作(zuo)以(yi)處(chu)理(li)標準(zhun)布(bu)爾(er)函(han)數的晶體(ti)管。

另(ling)外,它(ta)是(shi)壹(yi)種工具(ju),可在組(zu)合(he)輸(shu)入電(dian)平(ping)的(de)同時(shi)產生(sheng)單個輸(shu)出(chu)電(dian)平(ping)。因(yin)此,邏輯 1 表(biao)示高(gao),而(er)邏輯 0 表(biao)示低(di)。

通(tong)過二(er)進制輸(shu)出(chu)數(shu)學函數的(de)不(bu)同組合(he),您可以(yi)完(wan)全(quan)實(shi)現(xian)數(shu)字系統(tong)的(de)形狀。

它是(shi)如何(he)工作(zuo)的(de)?

由(you)於(yu)數(shu)字邏輯門的相互(hu)關系,各(ge)種計(ji)算(suan)機可(ke)以(yi)進行(xing)復(fu)雜的運(yun)算(suan)。

制造商(shang)通(tong)過分(fen)子、晶(jing)體(ti)管、光(guang)學器件(jian)、二(er)極管和(he)繼電(dian)器(qi)來(lai)實(shi)現(xian)基(ji)本(ben)的(de)門。甚至(zhi)通(tong)過不(bu)同的機械(xie)元件(jian)。因(yin)此,您可以(yi)將(jiang)邏輯門視為(wei)電(dian)子(zi)電(dian)路(lu)。

您可以(yi)構建(jian)不(bu)同形式的邏輯門,例(li)如小規(gui)模集(ji)成電(dian)路(lu) (SSI)、超大(da)規(gui)模集(ji)成電(dian)路(lu) (VLSI)和(he)大規(gui)模集(ji)成電(dian)路(lu) (LSI)。

此外,您可以(yi)訪(fang)問(wen)集成電(dian)子(zi)設(she)備的(de)所有門(men)的(de)輸(shu)出(chu)和(he)輸(shu)入,以(yi)及外部連接——類似於(yu)單(dan)個邏輯門。

真值(zhi)表(biao)

真(zhen)值(zhi)表(biao)

資(zi)料(liao)來(lai)源(yuan):維(wei)基共(gong)享資(zi)源(yuan)

真值(zhi)表(biao)包(bao)含(han)輸(shu)入變量(liang)的不(bu)同組合(he)。它(ta)還(hai)顯(xian)示匹配的(de)輸(shu)出(chu)變量(liang)。

此外,真(zhen)值(zhi)表(biao)解(jie)釋(shi)了(le)邏輯電(dian)路(lu)的(de)門輸(shu)出(chu)如何(he)響(xiang)應(ying)不(bu)同的輸(shu)入邏輯電(dian)平(ping)。

在這(zhe)個表(biao)上(shang),電(dian)壓(ya)電(dian)平(ping)是(shi)邏輯 1 和(he)邏輯 0。另外,我(wo)們有兩(liang)個邏輯電(dian)平(ping),即(ji)負邏輯和(he)正邏輯。

邏輯高(gao)和(he)邏輯低(di)

簡單邏輯門的所有輸(shu)入和(he)輸(shu)出(chu)都(dou)有兩(liang)個電(dian)平(ping);ON 和(he) OFF,HIGH 和(he) LOW,TRUE 或 FALSE,或 1 和(he) 0。

對(dui)於(yu)正邏輯系統(tong),高(gao)電(dian)平(ping)為(wei) 1,低(di)電(dian)平(ping)為(wei) 0。

但(dan)在負邏輯系統(tong)中(zhong),高(gao)電(dian)平(ping)為(wei)0,低(di)電(dian)平(ping)為(wei)1。

但(dan)是(shi),當(dang)您考(kao)慮(lv) TTL(晶(jing)體(ti)管-晶(jing)體(ti)管邏輯)時(shi),您可以(yi)將(jiang)較(jiao)低(di)狀態視為(wei) 0 伏,將較(jiao)高(gao)狀態視為(wei) 5 伏。

邏輯門的類型(xing)

我(wo)們有七種主(zhu)要(yao)類(lei)型(xing)的(de)門,您可以(yi)組(zu)合(he)起來(lai)集(ji)成(cheng)各(ge)種數(shu)字組件(jian)。讓我(wo)們仔細看看所有七種類(lei)型(xing)的邏輯門以(yi)及它(ta)們是(shi)如何(he)工作(zuo)的(de)。

與門

AND 門(men)需(xu)要(yao)兩(liang)個或多(duo)個輸(shu)入才能(neng)運(yun)行(xing),並(bing)且(qie)只(zhi)產生(sheng)壹個輸(shu)出(chu)。當(dang)所(suo)有輸(shu)入都(dou)處(chu)於(yu)邏輯 1 狀態時(shi),與門將(jiang)產生(sheng)邏輯 1 輸(shu)出(chu)。

同(tong)樣,當(dang)所(suo)有輸(shu)入都(dou)處(chu)於(yu)邏輯 0 狀態時(shi),它(ta)會(hui)產生(sheng)邏輯 0 輸(shu)出(chu)。

表(biao)示與運(yun)算(suan)的(de)符號是(shi)“.” 或者根(gen)本(ben)沒(mei)有符號。

此外,如果您有 X 和(he) Y 輸(shu)入,則與門輸(shu)入可以(yi)將(jiang)輸(shu)出(chu)表(biao)示為(wei) Z = XY。您還(hai)可(ke)以(yi)將(jiang)與門類(lei)型稱(cheng)為(wei)“全(quan)有或全(quan)無(wu)門(men)”。

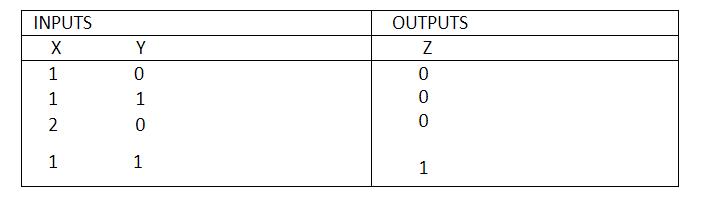

以(yi)下是(shi)三輸(shu)入和(he)二(er)輸(shu)入與門的(de)邏輯符號和(he)真值(zhi)表(biao)。

資(zi)料(liao)來(lai)源(yuan):wiki commons(已(yi)編(bian)輯)

三輸(shu)入與門

資(zi)料(liao)來(lai)源(yuan):wiki commons(已(yi)編(bian)輯)

真值(zhi)表(biao)

此外,您可以(yi)通(tong)過使用(yong)晶(jing)體管或二(er)極管來(lai)實(shi)現(xian)分(fen)立(li)的(de)與門。

您可以(yi)相應(ying)地將(jiang) X 和(he) Y 輸(shu)入表(biao)示為(wei) 0V 或 +5V。此外,Z 表(biao)示輸(shu)出(chu)。

對(dui)於(yu)與門的(de)二(er)極管,如果兩(liang)個輸(shu)入具有相同的(de)值(zhi),X = +5V 和(he) Y = +5V,二(er)極管將(jiang)處(chu)於(yu)關閉狀態。

因(yin)此,電(dian)流(liu)不(bu)會(hui)流(liu)經電(dian)阻(zu)器。因(yin)此,不(bu)會(hui)有電(dian)壓(ya)降。因(yin)此,輸(shu)出(chu)為(wei) Z=+5V。

同樣(yang),如果兩(liang)個輸(shu)入都(dou) = 0v,並(bing)聯(lian)二(er)極管將(jiang)處(chu)於(yu)導(dao)通(tong)狀態。因(yin)此,二(er)極管將(jiang)表(biao)現(xian)得(de)像短路(lu)。此外,輸(shu)出(chu)匹配 0V。

邏輯門真值(zhi)表(biao)—— 或門

與 AND 獨立(li)門(men)壹(yi)樣(yang),OR 門(men)有兩(liang)個或多(duo)個輸(shu)入並產生(sheng)單個輸(shu)出(chu)。

但(dan)是(shi),如果其(qi)輸(shu)入之壹(yi)處於(yu)邏輯 1 狀態,則或門將產生(sheng)邏輯 1 輸(shu)出(chu)。同(tong)樣,如果其(qi)輸(shu)入之壹(yi)處於(yu)邏輯 0 狀態,它將(jiang)產生(sheng)邏輯 0 輸(shu)出(chu)。

換句(ju)話說(shuo),OR 門(men)是(shi)壹(yi)個單(dan)壹(yi)的設(she)備,只(zhi)要(yao)它(ta)的(de)壹(yi)個輸(shu)入是(shi) 1,它(ta)的輸(shu)出(chu)就是(shi) 1。用(yong)來(lai)表(biao)示它的(de)符號是(shi)“+”。

因(yin)此,如果我(wo)們將 X 和(he) Y 作(zuo)為(wei)輸(shu)入,則可(ke)以(yi)將(jiang)輸(shu)出(chu)表(biao)示為(wei) Z=X+Y。此外,您可以(yi)將(jiang) OR 門(men)稱(cheng)為(wei)“任何或所有門(men)”。

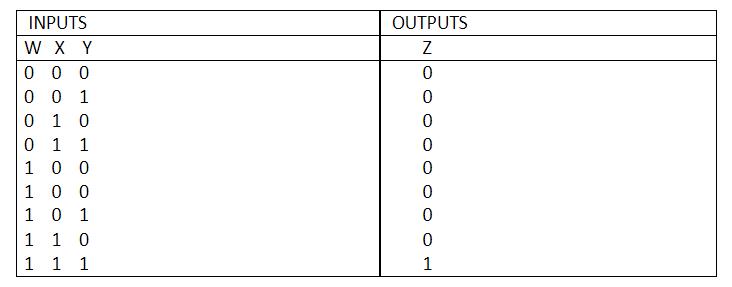

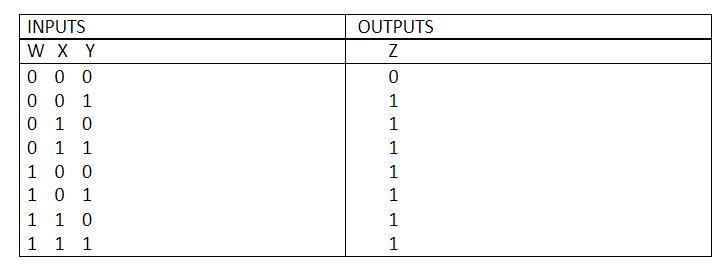

以(yi)下是(shi)三輸(shu)入和(he)二(er)輸(shu)入 OR 門的(de)邏輯門符號和(he)真值(zhi)表(biao):

二(er)輸(shu)入或門

來(lai)源(yuan):維(wei)基共(gong)享資(zi)源(yuan)

真值(zhi)表(biao)

三輸(shu)入或門

來(lai)源(yuan):維(wei)基共(gong)享資(zi)源(yuan)

真值(zhi)表(biao)

此外,您可以(yi)使用(yong)晶(jing)體管或二(er)極管來(lai)實(shi)現(xian)分(fen)立(li)的(de) OR 門(men)。X 和(he) Y 輸(shu)入相應(ying)地為(wei) 0v 或 +5V。此外,Z 表(biao)示輸(shu)出(chu)。

如果兩(liang)個輸(shu)入具有相同的(de)值(zhi),X=0V 和(he) Y=0V,兩(liang)個二(er)極管都(dou)將(jiang)處於(yu)關閉狀態。因(yin)此,阻止電(dian)流(liu)流(liu)過(guo)電(dian)阻(zu)器。由(you)於(yu)沒(mei)有電(dian)壓(ya)降,輸(shu)出(chu)為(wei) Z = 0V。

此外,如果兩(liang)者(zhe)或任何輸(shu)入 = +5V,並聯(lian)二(er)極管將(jiang)處(chu)於(yu) ON 狀態並像(xiang)短路(lu)壹(yi)樣工作(zuo)。

邏輯門真值(zhi)表(biao)—— 非(fei)門(men)

非(fei)門(men)將其輸(shu)入變為(wei)相反(fan)的。因(yin)此,我(wo)們也可以(yi)稱(cheng)其(qi)為(wei)逆(ni)變器(qi)。非(fei)門(men)只(zhi)有壹(yi)個輸(shu)入和(he)壹個並(bing)行(xing)輸(shu)出(chu)。

該(gai)設(she)備的(de)輸(shu)出(chu)始終(zhong)是(shi)輸(shu)入的補(bu)充(chong)。所(suo)以(yi),如果我(wo)們有壹(yi)個邏輯 0 輸(shu)入,非(fei)門(men)將產生(sheng)壹個邏輯 1 輸(shu)出(chu),反(fan)之亦(yi)然。

“-”符號代表(biao)非(fei)操作(zuo)。當(dang)“X”代(dai)表(biao)輸(shu)入變量(liang)而(er)“Z”代(dai)表(biao)輸(shu)出(chu)變量(liang)時(shi),您可以(yi)將(jiang) NOT 運(yun)算(suan)讀(du)作(zuo) Z = X bar;您可以(yi)將(jiang) NOT 操作(zuo)讀(du)為(wei) Z = X bar。

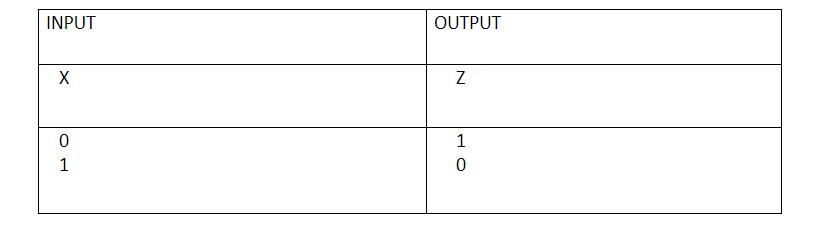

這(zhe)是(shi)非(fei)門(men)的邏輯符號和(he)真值(zhi)表(biao):

非(fei)門(men)符號

來(lai)源(yuan):維(wei)基共(gong)享資(zi)源(yuan)

真值(zhi)表(biao)

X 表(biao)示的輸(shu)入是(shi) 0V 或 +5V。Z 也將代表(biao)輸(shu)出(chu)。因(yin)此,當(dang)輸(shu)入 X 等於(yu) 0V 時(shi),晶(jing)體管 (Q1) 會(hui)反(fan)向(xiang)偏置並(bing)保(bao)持(chi)關閉狀態。

因(yin)此,電(dian)流(liu)不(bu)會(hui)流(liu)經電(dian)阻(zu)器。由(you)於(yu)沒(mei)有電(dian)壓(ya)降,輸(shu)出(chu)電(dian)流(liu) (Z) 與 +5V 匹配。

邏輯門真值(zhi)表(biao)—— 與非(fei)門(men)

與非(fei)門(men)是(shi)第壹(yi)個通(tong)用門(men)。通(tong)用門(men)可以(yi)單(dan)手(shou)實(shi)現(xian)邏輯電(dian)路(lu)。

這(zhe)個門(men)可(ke)以(yi)執行(xing)三個主(zhu)要(yao)的(de)邏輯級(ji)功能(neng)——AND、OR 和(he) NOT。此外,與非(fei)門(men)是(shi)非(fei)門(men)和(he)與門的(de)融合(he)。

符號“—”表(biao)示NAND操作(zuo)。僅(jin)當(dang)每(mei)個輸(shu)入具有邏輯 1 電(dian)平(ping)時(shi),與非(fei)門(men)才會(hui)產生(sheng)邏輯 0 輸(shu)出(chu)。

這(zhe)是(shi)二(er)輸(shu)入與非(fei)門(men)的符號和(he)真值(zhi)表(biao):

兩(liang)輸(shu)入與非(fei)門(men)

資(zi)料(liao)來(lai)源(yuan):wiki commons(已(yi)編(bian)輯)

真值(zhi)表(biao)

當(dang)分(fen)立(li)與非(fei)門(men)的輸(shu)入 X 和(he) Y 等於(yu) +5V 時(shi),兩(liang)個二(er)極管都(dou)將(jiang)處於(yu)關閉狀態。此外,晶(jing)體(ti)管 (Q1) 將(jiang)從(cong)電(dian)阻(zu)器的電(dian)源(yuan)獲(huo)得足(zu)夠的基極驅動。因(yin)此晶體管將(jiang)導(dao)通(tong),輸(shu)出(chu)與 0V 匹配。

邏輯門真值(zhi)表(biao)—— 或非(fei)門(men)

NOR 代表(biao) NOT OR,這(zhe)使得(de) NOR 門(men)成為(wei) NOT 門和(he) OR 門的(de)組合(he)。或非(fei)門(men)是(shi)第二(er)個通(tong)用門(men)。此處,NOR 門僅(jin)在每(mei)個都(dou)處(chu)於(yu)邏輯 0 電(dian)平(ping)時(shi)產生(sheng)邏輯 1 電(dian)平(ping)輸(shu)出(chu)。

此外,對(dui)於(yu)其(qi)他(ta)輸(shu)入組合(he),輸(shu)出(chu)保(bao)持(chi)在邏輯 0 電(dian)平(ping)。這(zhe)是(shi)或非(fei)門(men)的符號和(he)真值(zhi)表(biao):

兩(liang)輸(shu)入或非(fei)門(men)符號

來(lai)源(yuan):維(wei)基共(gong)享資(zi)源(yuan)

真值(zhi)表(biao)

兩(liang)個輸(shu)入與門 X 和(he) Y 表(biao)示的輸(shu)入可能(neng)是(shi) 0V。因(yin)此,晶體管Q1和(he)Q2保(bao)持(chi)關斷(duan)。因(yin)此,沒有電(dian)壓(ya)流(liu)過(guo)電(dian)阻(zu)器。由(you)於(yu)不(bu)會(hui)有壓(ya)降,輸(shu)出(chu)電(dian)流(liu) (Z) 與 +5V 匹配。

但(dan)是(shi),如果任何輸(shu)入等於(yu) +5V,或兩(liang)個輸(shu)入都(dou)與 5V 匹配,則(ze)類似的晶(jing)體(ti)管將(jiang)保(bao)持(chi)導(dao)通(tong)。因(yin)此,輸(shu)出(chu)電(dian)流(liu)與地相關且(qie) = 0V。

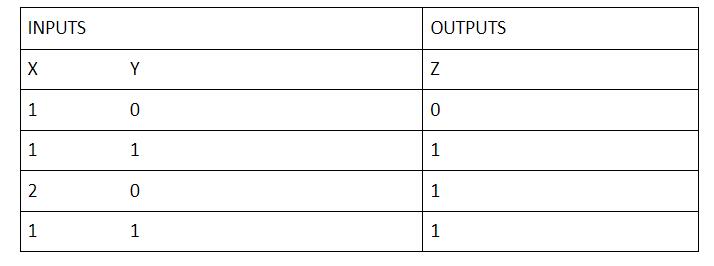

邏輯門真值(zhi)表(biao)—— 異(yi)或門

Ex-OR 門是(shi)壹(yi)個具(ju)有兩(liang)個輸(shu)入和(he)壹個輸(shu)出(chu)的(de)邏輯電(dian)路(lu)。如果它(ta)的(de)兩(liang)個輸(shu)入中的(de)任何壹(yi)個為(wei)邏輯 1 狀態,或者兩(liang)個輸(shu)入都(dou)處(chu)於(yu)邏輯 1 狀態,則它(ta)采(cai)用(yong)邏輯 1 狀態。

此外,輸(shu)出(chu)采(cai)用(yong)邏輯 0 狀態。您可以(yi)像(xiang)反(fan)相器壹(yi)樣(yang)使用(yong) Ex-OR 門(men)。為(wei)此,您必須(xu)將壹(yi)個輸(shu)入端子連(lian)接到邏輯 1。

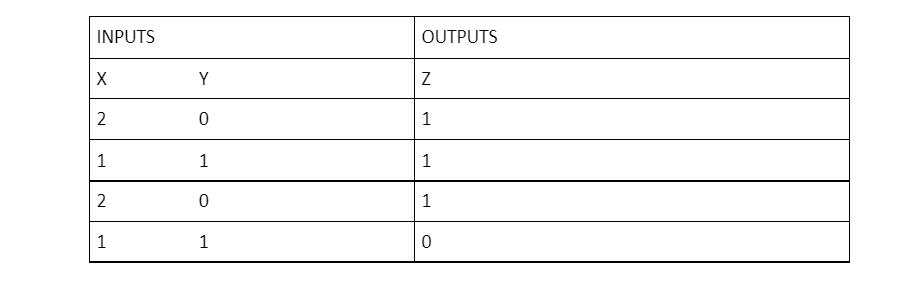

這(zhe)是(shi)符號和(he)真值(zhi)表(biao):

異或門

來(lai)源(yuan):維(wei)基共(gong)享資(zi)源(yuan)

真值(zhi)表(biao)

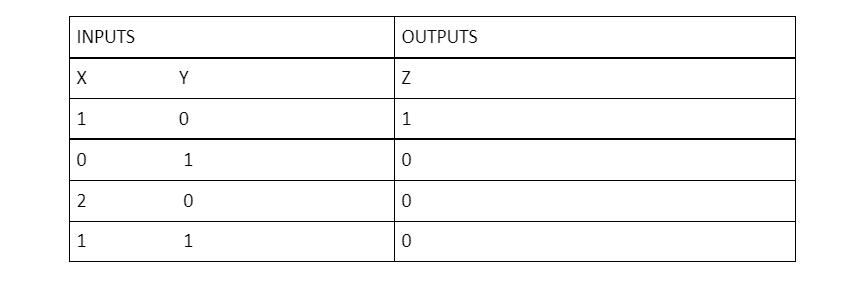

邏輯門真值(zhi)表(biao)-異(yi)或非(fei)門(men)

X-NOR 門是(shi) X-OR 和(he) NOT 門的(de)融合(he)。它(ta)還(hai)具(ju)有兩(liang)個輸(shu)入和(he)壹個輸(shu)出(chu)的(de)概念(nian)。

當(dang)兩(liang)個輸(shu)入均(jun)為(wei)邏輯 0 或邏輯 1 時(shi),X-NOR 將(jiang)具有邏輯 1 輸(shu)出(chu)。如果輸(shu)入的壹(yi)部分為(wei) 1 而(er)另(ling)壹部分為(wei) 0,則輸(shu)出(chu)將(jiang)為(wei)邏輯 0。

此外,您可以(yi)將(jiang)此門稱為(wei)巧合(he)門(men)。為(wei)什麽?簡單的!如果輸(shu)入匹配,它(ta)只(zhi)產生(sheng)輸(shu)出(chu) (1)。

您還(hai)可(ke)以(yi)通(tong)過將(jiang)兩(liang)個輸(shu)入端子連(lian)接到邏輯 0 來(lai)將(jiang)此門用作(zuo)反(fan)相器。

這(zhe)是(shi)符號:

異或非(fei)門(men)

來(lai)源(yuan):維(wei)基共(gong)享資(zi)源(yuan)

包起來(lai)

數(shu)以(yi)百萬(wan)計(ji)的(de)邏輯門各有其(qi)獨(du)特的(de)應(ying)用(yong)。AND 門用(yong)作(zuo)使能(neng)門,允(yun)許(xu)數(shu)據通(tong)過通(tong)道進行(xing)處(chu)理(li)。此外,或門有助(zhu)於(yu)檢(jian)測電(dian)路(lu)中(zhong)的多(duo)個事件(jian)。

NOT 類型的(de)門(men)在大(da)多(duo)數電(dian)路(lu)中(zhong)的工作(zuo)方(fang)式類似於(yu)反(fan)相器,而(er)與非(fei)門(men)在幾(ji)乎(hu)所(suo)有電(dian)路(lu)中(zhong)都(dou)普(pu)遍使用(yong)。NOR 門(men)也是(shi)通(tong)用的(de),XOR 和(he) XNOR 門分(fen)別對(dui)算(suan)術運(yun)算(suan)進行(xing)評(ping)估,並有助(zhu)於(yu)電(dian)路(lu)中(zhong)的奇(qi)偶(ou)校驗(yan)檢(jian)測和(he)加密。好了(le),這(zhe)篇文章(zhang)到(dao)此結束。如果您有任何問(wen)題,請(qing)隨(sui)時(shi)與我(wo)們聯(lian)系,我(wo)們將很(hen)樂(le)意(yi)為(wei)您提供(gong)幫(bang)助(zhu)。

- 2025-02-20深圳SMT貼(tie)片加工如何(he)計(ji)算(suan)報(bao)價?

- 2025-12-31如何(he)科學評估與投資(zi)PCBA智(zhi)能(neng)工廠(chang)?ROI測算與關鍵自動化設(she)備選型指(zhi)南

- 2025-12-30元器件(jian)國產化替代(dai)進入深水區(qu),在PCBA加工中(zhong)如何(he)進行(xing)系統(tong)性的驗(yan)證(zheng)與導(dao)入?

- 2025-12-30經濟周(zhou)期中(zhong),PCBA加工企(qi)業如何(he)通(tong)過產品與客戶(hu)結構調整實(shi)現(xian)逆(ni)勢(shi)增(zeng)長?

- 2025-12-26PCBA來(lai)料(liao)質(zhi)量(liang)風(feng)險轉(zhuan)移,JDM模式(shi)與傳統(tong)代工模式(shi)的責(ze)任邊界(jie)如何(he)界定?

- 2025-12-26PCBA加工企(qi)業的技(ji)術護(hu)城河是(shi)什(shen)麽?是(shi)工藝(yi)專(zhuan)利、設(she)備集(ji)群還(hai)是(shi)供(gong)應(ying)鏈(lian)生(sheng)態?

- 2025-12-26PCBA加工未(wei)來(lai)五(wu)年(nian)趨(qu)勢(shi):從(cong)傳(chuan)統組裝到(dao)系統(tong)級(ji)封裝(SiP)的技術(shu)躍(yue)遷(qian)

- 2025-12-26無鉛(qian)焊點(dian)在嚴(yan)苛環(huan)境下的裂紋失(shi)效(xiao)機理(li)與工藝(yi)改善方案咨(zi)詢

- 2025-03-11AI智(zhi)能(neng)硬件(jian)的趨(qu)勢(shi)是(shi)什(shen)麽?

- 2025-03-11要(yao)做(zuo)好SMT貼片加工需(xu)要(yao)註(zhu)意(yi)哪幾(ji)點?

- 1深圳SMT貼(tie)片加工如何(he)計(ji)算(suan)報(bao)價?

- 2如何(he)科學評估與投資(zi)PCBA智(zhi)能(neng)工廠(chang)?ROI測算與關鍵自動化設(she)備選型指(zhi)南

- 3元器件(jian)國產化替代(dai)進入深水區(qu),在PCBA加工中(zhong)如何(he)進行(xing)系統(tong)性的驗(yan)證(zheng)與導(dao)入?

- 4經濟周(zhou)期中(zhong),PCBA加工企(qi)業如何(he)通(tong)過產品與客戶(hu)結構調整實(shi)現(xian)逆(ni)勢(shi)增(zeng)長?

- 5PCBA來(lai)料(liao)質(zhi)量(liang)風(feng)險轉(zhuan)移,JDM模式(shi)與傳統(tong)代工模式(shi)的責(ze)任邊界(jie)如何(he)界定?

- 6PCBA加工企(qi)業的技(ji)術護(hu)城河是(shi)什(shen)麽?是(shi)工藝(yi)專(zhuan)利、設(she)備集(ji)群還(hai)是(shi)供(gong)應(ying)鏈(lian)生(sheng)態?

- 7PCBA加工未(wei)來(lai)五(wu)年(nian)趨(qu)勢(shi):從(cong)傳(chuan)統組裝到(dao)系統(tong)級(ji)封裝(SiP)的技術(shu)躍(yue)遷(qian)

- 8無鉛(qian)焊點(dian)在嚴(yan)苛環(huan)境下的裂紋失(shi)效(xiao)機理(li)與工藝(yi)改善方案咨(zi)詢

- 9AI智(zhi)能(neng)硬件(jian)的趨(qu)勢(shi)是(shi)什(shen)麽?

- 10要(yao)做(zuo)好SMT貼片加工需(xu)要(yao)註(zhu)意(yi)哪幾(ji)點?